完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > FPGA設計

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。

fpga你可以理解成把一堆邏輯器件比如與門,或門,選擇器等放在一個盒子里,盒子周圍就是片子的引腳。通過邏輯編寫,把許多的門和許多選擇器等器件串聯或并聯引腳上。就等于把數電實驗在fpga里面做。

arm的編程指的是c語言或者匯編的編程,arm一條條的讀取語句,順序實現其功能。

fpga的編程則完全不同。fpga編程本身指的就是編輯其內部的電路結構。fpga運行代碼也不是一條條執行的,而是讀入代碼之后就生成了邏輯門結構。這些邏輯門結構是并行運作的。給輸入就同時產生輸出。所以fpga的編程語言叫做hdl(硬件描述語言)。hdl中的語句執行是不分先后的。

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

開發

FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入門較難。目前國內有專業的FPGA外協開發廠家,如[北京中科鼎橋ZKDQ-TECH]等。FPGA開發需要從頂層設計、模塊分層、邏輯實現、軟硬件調試等多方面著手。

FPGA怎么理解

fpga你可以理解成把一堆邏輯器件比如與門,或門,選擇器等放在一個盒子里,盒子周圍就是片子的引腳。通過邏輯編寫,把許多的門和許多選擇器等器件串聯或并聯引腳上。就等于把數電實驗在fpga里面做。

arm的編程指的是c語言或者匯編的編程,arm一條條的讀取語句,順序實現其功能。

fpga的編程則完全不同。fpga編程本身指的就是編輯其內部的電路結構。fpga運行代碼也不是一條條執行的,而是讀入代碼之后就生成了邏輯門結構。這些邏輯門結構是并行運作的。給輸入就同時產生輸出。所以fpga的編程語言叫做hdl(硬件描述語言)。hdl中的語句執行是不分先后的。

工程師談:FPGA設計之硬件

做FPGA也有兩年了,從剛開始的Verilog開始學起,到后來的最小系統,再到颶風II代開發板設計,到現在的XILINX XC2C系列CPLD開發,覆蓋了硬件設計底層的一些經驗。其實自己很想玩下FPGA的嵌入式,覺得很有前途的,但是后來自己也只是在學校開發板上過了下癮。談談如何玩FPGA吧

要了解FPGA首先弄懂它的結構,FPGA是基于LUT結構,在器件選型的時候一般是參考它的邏輯單元的大小,然后是功耗和匹配電平的關系,IO口供電電平;內部PLL供電電平;所有的FPGA工作電壓都是在3.3V,2.5V,1.2V三者之間選擇,當然一定要弄清楚IO口是基于CMOS還是TTL工藝的,兩者不能混淆。

選好器件后,接下來是原理圖設計。在原理圖設計中一般要注意去耦電容的容值大小,時鐘電路,內部鎖相環電路,下載電路。一般AS下載電路還要注意匹配的配置芯片的大小,在器件手冊上都能查到,所以在設計前一定要通讀對應的器件手冊,一般的配置電路手冊上都有參考,少走很多彎路。設計好原理圖后一般要考慮下面IO口的接法:GCLK/GRST;這些復用的管腳一般不用作普通的IO口。而用作對應的第二功能。

原理圖設計好后重點是PCB的設計,在設計前一定要反復檢查原理圖,是否有原理上的錯誤,一定注意電源電路的設計完整性。對于一般的TQFP封裝的芯片要注意采用雙面板我習慣把電源放在底層,濾波電容也通過過孔置于底層,在設計中當然是先布電源,時鐘,最后布信號線了,其中的一些小的細節不用我啰嗦了,想必各位比我還厲害了。

完成整個硬件電路板的設計后,接下來就是程序的設計了,這里面靈活性很大,在設計中一定要注意語法的嚴謹性,一個小小的“《=“都會帶來無盡的麻煩,在完成程序設計后,一定要進行時序仿真,我一般是先把模塊分塊利用工具內部波形仿真來查看時序,接著采用SIGNAL TAP II進行內部邏輯分析,這個花了太多時間了,一個仿真就要幾個小時。所以還是用TESTBENCH比較實際,注意是測試信號建立時間保持時間是否滿足時序要求。

設計可靠的可編程邏輯門陣列(FPGA)對于不容故障的系統來說是一項具有挑戰性的任務。本文介紹FPGA設計的復雜性,重點關注如何在提高可靠性的同時管理隨之...

使用Altera Interface Planner高效設計FPGA引腳布局

Altera Interface Planner 用于探索設備的外設架構,并高效地分配接口。通過實時進行擬合和合法性檢查,防止非法引腳分配。

異步復位異步釋放會有什么問題?FPGA異步復位為什么要同步釋放呢?

一般來說,復位信號有效后會保持比較長一段時間,確保 register 被復位完成。但是復位信號釋放時,因為其和時鐘是異步的關系,我們不知道它會在什么時刻被釋放。

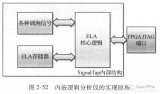

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

對于FPGA調試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環境下進行仿真和調試,開發板類型EP4CE15F17。

高云EDA FPGA設計已通過ISO 26262和IEC 61508功能安全標準認證

GOWIN中密度和低密度FPGA的高安全性和高可靠性促使汽車OEM將其設計用于視頻橋接、顯示驅動和圖像信號處理等應用中。

AMD Vivado Design Suite 2023.2的優勢

由于市場環境日益復雜、產品競爭日趨激烈,為了加快推出新型自適應 SoC 和 FPGA 設計,硬件設計人員和系統架構師需要探索更為高效的全新工作方式。AM...

fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據?

fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據? 在FPGA設計中,通常需要跨時鐘域進行數據通信。跨時鐘域通信就是在不同的時鐘域之間傳輸數據...

安全當前已成為各垂直市場所有設計的當務之急。今天,有進一步證據向系統架構師和設計人員證明,使用Microchip Technology Inc.(美國微...

業界高端FPGA的卓越性能和高口碑聲譽都有哪些因素了?其中很重要的一個因素就是FPGA內部豐富的時鐘資源使得FPGA在處理復雜時鐘結構和時序要求的設...

? 這是筆者去年某個時間節點的感悟,由于工作繁忙,寫完后擱置一邊了。而對于“設計最優化”這個議題,筆者也一直深感功力不夠,不敢多做闡釋。但是,不管怎樣,...

虹科干貨 | 如何測試與驗證復雜的FPGA設計(3)——硬件測試

仿真和驗證是開發任何高質量的基于FPGA的RTL編碼過程的基礎。在前文中,我們介紹了面向實體/塊的仿真,并介紹了如何在虹科的IP核中執行面向全局的仿真。...

2022-06-18 標簽:FPGA設計 1444 0

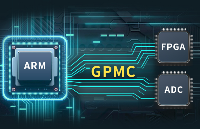

為何TI的GPMC并口,更常被用于連接FPGA、ADC?我給出3個理由

1GPMC并口簡介GPMC(GeneralPurposeMemoryController)是TI處理器特有的通用存儲器控制器接口,是AM335x、AM4...

熱分析的最終目標是要使得整個系統能夠穩定地運行,特別是保證芯片的結溫不能超過安全閾值。如果無法保證這一點,那么FPGA芯片在性能指標、可靠性、使用壽命等...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題 教程专题

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |