完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > RTL

RTL在電子科學中指的是寄存器轉換級電路(Register Transfer Level)的縮寫,也叫暫存器轉移層次。

在集成電路設計中, register-transfer level(RTL)是用于描述同步數字電路操作的抽象級。

在RTL級,IC是由一組寄存器以及寄存器之間的邏輯操作構成。之所以如此,是因為絕大多數的電路可以被看成由寄存器來存儲二進制數據、由寄存器之間的邏輯操作來完成數據的處理,數據處理的流程由時序狀態機來控制,這些處理和控制可以用硬件描述語言來描述。

RTL級和門級簡單的區別在于,RTL是用硬件描述語言(Verilog 或VHDL)描述理想達到的功能,門級則是用具體的邏輯單元(依賴廠家的庫)來實現你的功能,門級最終可以在半導體廠加工成實際的硬件,一句話,RTL和門級是設計實現上的不同階段,RTL經過邏輯綜合后,就得到門級。

RTL描述是可以表示為一個有限狀態機,或是一個可以在一個預定的時鐘周期邊界上進行寄存器傳輸的更一般的時序狀態機,通常VHDL/verilog兩種語言進行描述。

RTL在電子科學中指的是寄存器轉換級電路(Register Transfer Level)的縮寫,也叫暫存器轉移層次。

寄存器傳輸級

在集成電路設計中, register-transfer level(RTL)是用于描述同步數字電路操作的抽象級。

在RTL級,IC是由一組寄存器以及寄存器之間的邏輯操作構成。之所以如此,是因為絕大多數的電路可以被看成由寄存器來存儲二進制數據、由寄存器之間的邏輯操作來完成數據的處理,數據處理的流程由時序狀態機來控制,這些處理和控制可以用硬件描述語言來描述。

RTL級和門級簡單的區別在于,RTL是用硬件描述語言(Verilog 或VHDL)描述理想達到的功能,門級則是用具體的邏輯單元(依賴廠家的庫)來實現你的功能,門級最終可以在半導體廠加工成實際的硬件,一句話,RTL和門級是設計實現上的不同階段,RTL經過邏輯綜合后,就得到門級。

RTL描述是可以表示為一個有限狀態機,或是一個可以在一個預定的時鐘周期邊界上進行寄存器傳輸的更一般的時序狀態機,通常VHDL/verilog兩種語言進行描述。

RTL電路是最早研制成功的一種有實用價值的集成電路。有N 個門的輸入端并接在DCTL電路輸出端,因為DCTL電路輸出端門的晶體管基極導通電壓,電流曲線并不能完全一致,并聯在一起,輸入電流易出現分配不均勻的現象。輸入電流小的負載門可能得不到足夠的基極驅動電流,達不到飽和,從而輸出端可能從應有的“0”態改變到“1”狀態,使系統出現差錯。負載輸入端并接越多,產生電流分配不勻的可能性越大。這種現象叫作“搶電流”。RTL電路是每一輸入級基極串接一個電阻,旨在得到改善和補償,使基極輸入電流 Ib對基極-發射極V公式 符號-Ib特性的依賴性小一些。根據 Rb的阻值即可確定RTL電路的最大負載門數。

RTL電路結構簡單,元件少。RTL電路的嚴重缺點是基極回路有電阻存在,從而限制了電路的開關速度,抗干擾性能也差,使用時負載又不能過多。RTL電路是一種飽和型電路,只適用于低速線路,實際上已被淘汰。為了改善RTL邏輯電路的開關速度,在基極電阻上再并接一個電容,就構成了電阻-電容-晶體管邏輯電路(RCTL)。有了電容,不僅可以加快開關速度,而且還可以加大基極電阻,從而減小電路功耗。但是,大數值電阻和電容在集成電路制造工藝上要占去較大的芯片面積,而且取得同樣容差值的設計也比較困難。因此,RCTL電路實際上也沒有得到發展。

行為級和RTL級的區別

RTL級,registertransferlevel,指的是用寄存器這一級別的描述方式來描述電路的數據流方式;而Behavior級指的是僅僅描述電路的功能而可以采用任何verilog語法的描述方式。鑒于這個區別,RTL級描述的目標就是可綜合,而行為級描述的目標就是實現特定的功能而沒有可綜合(可實現)的限制。

行為級是RTL的上一層,行為級是最符合人類邏輯思維方式的描述角度,一般基于算法,用C/C++來描述。從行為級到RTL級的轉換,一般都是由IC設計人員手工翻譯。

這個過程繁瑣,工作量很大,特別是隨著數字系統的復雜性提升,這樣的純手工“翻譯”過程容易出錯,且使得開發周期變長。一批高級綜合工具應運而生。如Menter Graphics的高層次綜合工具Catapult C Synthesis。能夠將數字系統的行為級描述映射為RTL設計,并滿足給定的目標限制。從層次由上到下,數字系統的設計過程為:

Idea-》行為級描述-》rtl描述-》門級網標-》物理版圖

行為級的描述更多的是采取直接賦值的形式,只能看出結果,看不出數據流的實際處理過程。其中又大量采用算術運算,延遲等一些無法綜合的語句。常常只用于驗證仿真。

RTL級的描述就會更詳細一些,并且從寄存器的角度,把數據的處理過程表達出來。可以容易地被綜合工具綜合成電路的形式。

行為級描述可是說是RTL的上層描述,比RTL更抽象。行為描述不關心電路的具體結構,只關注算法。

有行為綜合工具,可以直接將行為級的描述綜合為RTL級的,比如Behavioral Compiler。

在硬件設計中有一句著名的話:thinking of hardware。RTL在很大程度上是對流水線原理圖的描述。哪里是組合邏輯,哪里是寄存器,設計者應該了然于胸。組合邏輯到底如何實現,取決于綜合器和限制條件。

rtl級可以理解為,可以直接給綜合工具生成你要的網表的代碼,而行為級則不行。比如real(浮點實數?)可以用于行為級,而不能用于rtl級!

Behavior is for testbench for modelling.

RTL is for synthesis

語法塊如果可以被綜合到gate level,就是RTL的。否則就是behavior level的。

同樣是for語句,如果循環條件是常數,就是RTL的,如果是變量,就是behavior的。

RTL級描述數據在寄存器層次的流動模型。

always屬于行為級模型,是最基本的行為模型,是可以綜合的。

綜合與RTL或者行為級沒有必然聯系,雖然大多數行為模型不能綜合

從網上copy

目的區別:

行為級描述目的是加快仿真速度,做法是盡量減少一個always塊中要執行的語句數量,其結果不是為了綜合,只關注算法。有行為綜合工具,可以直接將行為級的描述綜合為RTL級的,比如Behavioral Compiler。

形式區別:

RTL級描述是為了綜合工具能夠正確的識別而編寫的代碼,verilog中有一個可綜合的子集,不同的綜合工具支持的也有所不同,RTL級的描述就會更詳細一些,并且從寄存器的角度,把數據的處理過程表達出來。可以容易地被綜合工具綜合成電路的形式。可以采用任何verilog語法的描述方式。鑒于這個區別,RTL級描述的目標就是可綜合,

行為級的描述更多的是采取直接賦值的形式,只能看出結果,看不出數據流的實際處理過程。其中又大量采用算術運算,延遲等一些無法綜合的語句。常常只用于驗證仿真。

電路區別:

RTL級,register transfer level,指的是用寄存器這一級別的描述方式來描述電路的數據流方式;RTL在很大程度上是對流水線原理圖的描述。哪里是組合邏輯,哪里是寄存器,設計者應該了然于胸。組合邏輯到底如何實現,取決于綜合器和限制條件。RTL是晶體管傳輸級,描述硬件的相互聯接關系,一般都可以綜合;

而Behavior級指的是僅僅描述電路的功能而在硬件設計中有一句著名的話:thinking of hardware。簡單說,rtl就是用寄存器和組合邏輯組成,不能再用其他construct;behavior就是指定輸入和輸出之間的關系。

混亂點:有時感覺RTL級是行為級與數據流級的混合應用。

樂點:同樣是for語句,如果循環條件是常數,就是RTL的,如果是變量,就是behavior的。

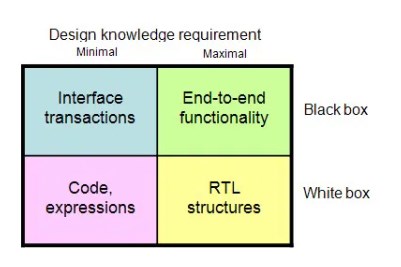

如何將SystemVerilog斷言屬性和覆蓋屬性置于在設計上?

功能覆蓋、激勵生成和運行管理是當今功能驗證的三大相互關聯的任務。其中,功能覆蓋率可以說是最重要的,主要是因為覆蓋率收斂是tape的主要標準。

在Windows 10上創建并運行AMD Vitis?視覺庫示例

本篇文章將演示創建一個使用 AMD Vitis? 視覺庫的 Vitis HLS 組件的全過程。此處使用的是 Vitis Unified IDE。如果您使...

在數字設計的Implementation過程中,從RTL到GDSII的每一步都是高度計算密集型的。

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

本文介紹了在 AMD Vivado? Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的過程中要把具體...

AMD Versal AI Edge自適應計算加速平臺之PL LED實驗(3)

對于Versal來說PL(FPGA)開發是至關重要的,這也是Versal比其他ARM的有優勢的地方,可以定制化很多ARM端的外設

英諾達(成都)電子科技有限公司隆重推出芯片設計早期RTL級功耗優化工具—EnFortius RTL Power Explorer(ERPE),該工具可以...

Cadence Verisium Debug:統一調試平臺,加速SoC設計

Cadence的統一調試平臺Verisium Debug,為從IP到SoC級別的復雜設計提供了全面的調試解決方案。該平臺集成了多種調試功能,包括RTL調...

當CPU算力趨近極限,GPU能否替代CPU滿足數字芯片設計的算力需求?

就數字設計實現而言,RTL-to-GDSII流程中的每一步都涉及海量計算。在SoC級別,開發者需要評估數百個分區的各種版圖規劃選項,從而更大限度減少互連...

上海科學技術委員會發布2024年第一批上海市高新技術成果轉化項目名單,立芯“LePlace布局及物理優化軟件”項目成功通過認定。

Multi-Die系統驗證很難嗎?Multi-Die系統驗證的三大挑戰

在當今時代,摩爾定律帶來的收益正在不斷放緩,而Multi-Die系統提供了一種途徑,通過在單個封裝中集成多個異構裸片(小芯片),能夠為計算密集型應用降低...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題 教程专题

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |