完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > ip核

IP就是知識(shí)產(chǎn)權(quán)核或知識(shí)產(chǎn)權(quán)模塊的意思,在EDA技術(shù)開發(fā)中具有十分重要的地位。美國(guó)著名的Dataquest咨詢公司將半導(dǎo)體產(chǎn)業(yè)的IP定義為“用于ASIC或FPGA中的預(yù)先設(shè)計(jì)好的電路功能模塊”。

文章:335個(gè) 瀏覽:50183次 帖子:249個(gè)

ZYNQ PS + PL異構(gòu)多核案例開發(fā)手冊(cè)之1axi_gpio_led_demo案例

本文主要介紹ZYNQ PS + PL異構(gòu)多核案例的使用說明,適用開發(fā)環(huán)境:Windows 7/10 64bit、Xilinx Vivado 2017.4...

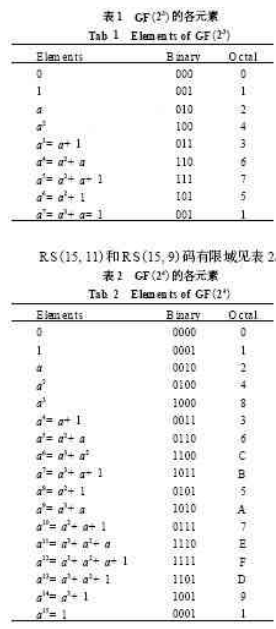

在編碼電路中實(shí)現(xiàn)RS碼編碼器IP核的應(yīng)用設(shè)計(jì)

數(shù)字信號(hào)在傳輸過程中可能受到各種干擾及信道傳輸特性不理想的影響而使信號(hào)發(fā)生錯(cuò)誤, 從而接收到錯(cuò)誤的信息。為了實(shí)現(xiàn)數(sh...

在嵌入FPGA的IP核8051微處理器上實(shí)現(xiàn)UIP協(xié)議棧的設(shè)計(jì)方法

在FPGA中植入8051后, 還可在上面實(shí)現(xiàn)簡(jiǎn)單的TCP/IP協(xié)議, 以支持遠(yuǎn)程訪問或進(jìn)行遠(yuǎn)程調(diào)試, 這只是在...

基于JavaCAD架構(gòu)的安全性與IP保護(hù)研究

目前,基于IP的EDA設(shè)計(jì)流程面臨著兩大挑戰(zhàn)。首先,必須提供方法技術(shù),用于測(cè)試包含IP組件設(shè)計(jì)的可靠性和質(zhì)量;另一方面,必須...

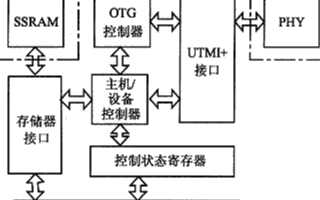

基于處理器實(shí)現(xiàn)USB 0TG控制器芯片的IP核應(yīng)用設(shè)計(jì)

OTGl.Oa補(bǔ)充規(guī)范對(duì)USB2.O進(jìn)行的最重要擴(kuò)展是其更具節(jié)能性、電源管理,并允許設(shè)備以主機(jī)和外設(shè)2種形式工作。...

基于多密碼算法IP核集成方法實(shí)現(xiàn)安全芯片功能多樣化

信息社會(huì)中,基于密碼算法設(shè)計(jì)的安全芯片,能夠?yàn)橛脩舻拿舾行畔⑻峁┯行У臋C(jī)密性與完整性保護(hù)。信息化的不斷深入使得人們對(duì)信息安全服務(wù)...

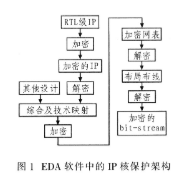

基于現(xiàn)場(chǎng)可編程門陣列技術(shù)和EDA技術(shù)實(shí)現(xiàn)IP核的設(shè)計(jì)方案

在EDA軟件的處理流程中,EDA軟件必須能夠正確解析設(shè)計(jì),才能完成處理,因此設(shè)計(jì)本身對(duì)于EDA軟件是公開的。這里假定EDA軟件是可信的。具有IP核保護(h...

基于Xilinx Spartan II系列FPGA器件實(shí)現(xiàn)IP核的設(shè)計(jì)

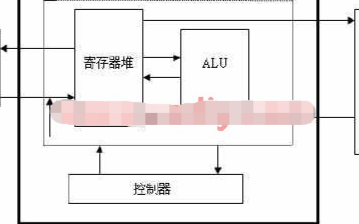

精簡(jiǎn)指令集計(jì)算機(jī)RISC(Reduced Instruction Set Computer)是針對(duì)復(fù)雜指令集計(jì)算機(jī)CISC(Complex...

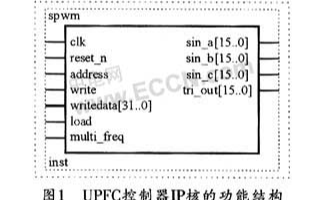

使用Altera CycloneIIEP2C35評(píng)估板實(shí)現(xiàn)UPFC控制器IP核的設(shè)計(jì)

UPFC控制器的IP主要用來輸出3路相位分別相差2π/3的正弦波形數(shù)據(jù)和3路相位分別相差2π/3的三角載波波形數(shù)據(jù)。由于UPFC控制系統(tǒng)采用SPWM調(...

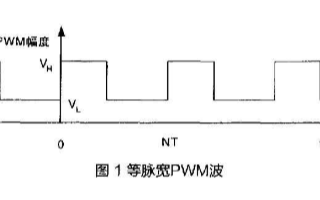

CorePWM的原理及采用FPGA技術(shù)實(shí)現(xiàn)PWM IP核的設(shè)計(jì)

脈沖寬度調(diào)制(PWM) 是英文“Pluse Width Modulation”的縮寫,簡(jiǎn)稱脈寬調(diào)制。它是利用微處理器的數(shù)字輸出來對(duì)模擬電路進(j...

基于FPGA技術(shù)實(shí)現(xiàn)圖像增強(qiáng)數(shù)據(jù)的仿真實(shí)驗(yàn)分析

Xilinx的Vivado中集成的圖像增強(qiáng)(Image Enhancement)IP可以有效降低圖像噪聲并增強(qiáng)圖像邊緣。該IP使用了2D濾波方式,可以在...

基于片上可編程系統(tǒng)解決方案實(shí)現(xiàn)視頻編解碼IP核的設(shè)計(jì)

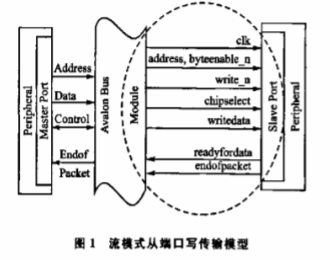

SOPC是Altera公司提出的片上可編程系統(tǒng)解決方案,它將CPU、存儲(chǔ)器、I/O接口、DSP模塊以及鎖相環(huán)的系統(tǒng)設(shè)計(jì)所必需的模塊集成到...

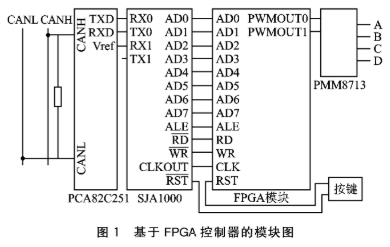

基于FPGA的VHDL語(yǔ)言設(shè)計(jì)控制器SJA1000的IP軟核設(shè)計(jì)

分析了CAN控制器SJA1000的特點(diǎn)及CAN協(xié)議通信格式。設(shè)計(jì)了控制器SJA1000的IP軟核,能為應(yīng)用提供一個(gè)性能優(yōu)良的、易于...

基于Nios II系統(tǒng)實(shí)現(xiàn)LCD顯示控制IP核的設(shè)計(jì)

基于NiosII 軟核的SOPC(System ON Programmable Chip)是Altera 公司提出的片上可編程系統(tǒng)解決方案,它將CPU、...

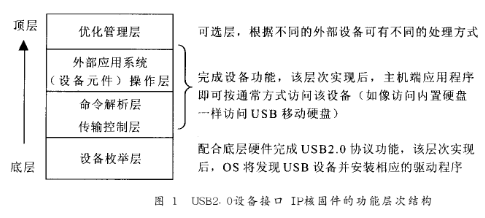

USB2.0設(shè)備接口IP核的設(shè)計(jì)實(shí)用性分析

USB2.0規(guī)范的推出極大地刺激了包括各類計(jì)算機(jī)外設(shè)在內(nèi)的多種電子消費(fèi)產(chǎn)品的開發(fā)設(shè)計(jì), USB已成為微機(...

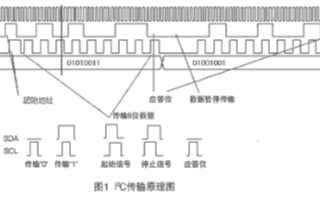

I2C串行擴(kuò)展通信的特點(diǎn)及實(shí)現(xiàn)IP核的設(shè)計(jì)

由于CPLD數(shù)字設(shè)計(jì)結(jié)構(gòu)化的趨勢(shì),將出現(xiàn)針對(duì)CPLD不同層次的IP(Intellectual Property)核。各個...

學(xué)完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內(nèi)已經(jīng)集成了相應(yīng)的IP核來控制這些SDRAM,.....

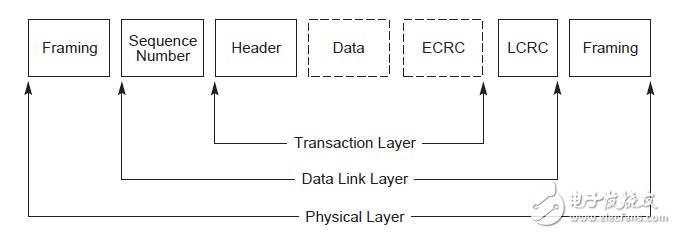

PCI-Express(peripheral component interconnect express)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),它原來的...

賽靈思--縮短開發(fā)時(shí)間,支持高速模數(shù)/數(shù)模串行接口

賽靈思公司無線通信副總裁Sunil Kar指出:“我們很高興我們的產(chǎn)品能成為NEC iPASOLINK毫米波通信系統(tǒng)的一部分,并助力構(gòu)建出高可靠性網(wǎng)絡(l...

2019-07-24 標(biāo)簽:數(shù)據(jù)傳輸IP核移動(dòng)無線網(wǎng)絡(luò) 2430 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題 教程专题

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |