完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發(fā)燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態(tài)的最佳平臺。

上位機才能夠在接收數據后正確顯示圖像。所以每幀圖像的開始需要多傳輸8字節(jié)數據,一般規(guī)定每次傳輸一行數據,由于OV7725一行有640個像素,每個像素16位,而以太網每個時鐘傳輸8位數據,因此需要1280個時鐘才能傳輸完一次數據。...

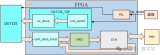

AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協(xié)處理器接口(AXI4-Lite)、AXI主外設接口(AXI4)、AXI外設到主處理器接口(AXI4-Lite)等。...

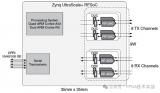

以核心處理板為核心,由信號源產生的待處理模擬信號通過同軸線纜連接到核心處理板的信號接口,同時,連接同步時鐘等其他相關信號到核心處理板。...

一般都是先創(chuàng)建MIF文件,將圖像中的像素信息用一個ROM儲存起來,然后調用ROM里面的地址進行處理,相當于制作了一個ROM查找表。...

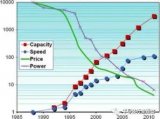

了解FPGA器件何時適合實現(xiàn)所需的系統(tǒng)功能是理解FPGA技術的關鍵要素。設計團隊明白FPGA技術并不適用于每一個設計或應用程序。...

我們都知道RAM是根據地址查找對應的數據,而對于CAM,則恰好相反,是已知數據查找其對應的地址。像在網絡報文處理里,根據報文的五元組的一些信息去查詢其所屬的規(guī)則地址,隨后通過該地址去查詢對應的RAM獲取對應的Action信息。...

FPGA 被封裝在更大的封裝中,從而提供了更多的 I/O。"然而,I/O 的增加并不像邏輯資源那樣引人注目。...

數據轉換功能的集成為5G基站中的遠程無線單元(RRU)提供了巨大的節(jié)能效果。對于每個JESD204通道,節(jié)省的成本大約為1W,或者對于來自天線陣列的每個數據流來說,節(jié)省的成本是不同的。...

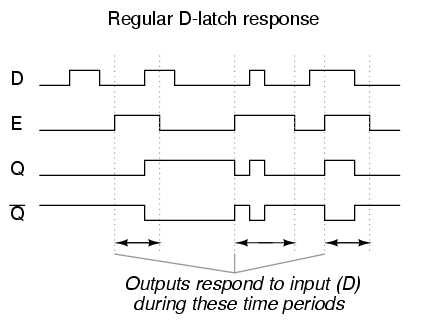

鎖存器、觸發(fā)器和寄存器它們的英文分別為:Latch、Flip-Flop、Register。我們對這三個單詞的翻譯真的是非常直觀,從名字就能大概猜出它們的含義。...

科通技術了解到AnDAPT電源解決方案的目標市場是電源軌數量較多的市場,因此需要電源管理功能,并通過AnDAPT產品線幫助AMD產品線的客戶簡化電源設計。...

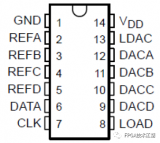

本設計采用串行數/模轉換芯片TLC5620,TLC5620是一個擁有四路輸出的數/模轉換器,時鐘頻率最大可達到1MHz。...

FPGA 正是一種硬件可重構的體系結構。它的英文全稱是Field Programmable Gate Array,中文名是現(xiàn)場可編程門陣列。 FPGA常年來被用作專用芯片(ASIC)的小批量替代品,然而近年來在微軟、百度等公司的數據中心大規(guī)模部署,以同時提供強大的計算能力和足夠的靈活性。...

首先是FPGA硬件的變化太多,各個模塊可配參數的變化(比如卷積模塊并行數的變化),另外一個是網絡模型多種多樣以及開源的網絡模型平臺也很多(tensorflow,pytorch等)。網絡壓縮也有很多種算法,這些算法基本上都會導致網絡模型精度的降低。...

DNN中應用最廣泛的是CNN和RNN,CNN是一種卷積網絡,在圖片識別分類中用的較多,RNN可以處理時間序列的信息,比如視頻識別和語音識別。...

在設計過程的每個階段,設計者均可以打開Vivado集成開發(fā)環(huán)境,對存儲器中保存的當前設計進行分析和操作。...

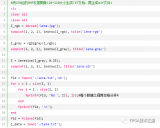

將設置設計的輸出路徑,設置設計輸出路徑的步驟如下所示。 第一步:如圖4.3所示,在“Vivado%”提示符后輸入命令“set outputDir ./gate_Created_Data/top_output”。...

為了避免每次SPI驅動重寫,直接參數化,盡量一勞永逸。SPI master有啥用呢,你發(fā)現(xiàn)各種外圍芯片的配置一般都是通過SPI配置的,只不過有三線和四線。...

HDR 內容和顯示實際上包括三個考慮因素:動態(tài)范圍、光電/電光傳遞函數(OETF/EOTF) 和寬色域。 HDR 提供了從黑色到白色的更大范圍,或通常所稱的更白的白色或更黑的黑色。...

FPGA本質是一種可編程的芯片。可以把硬件設計重復燒寫在它的可編程存儲器里,從而使FPGA芯片可以執(zhí)行不同的硬件設計和功能。...

隨著ASIC向SoC轉移,可編程邏輯供應商開發(fā)了可編程SoC。這絕對不是在數據通信領域如此流行的數據吞吐量引擎,也不是門陣列。...