我看到ADS1278上寫輸入參看電壓2.5V,輸入共模電壓2.5V。一般輸入共模電壓不是一個范圍嗎,為什么是一個確定的數(shù)了?我現(xiàn)在混亂了。

2024-03-08 10:56:54

請教一下基礎知識 共模電壓 同時加在電壓表兩測量端和規(guī)定公共端之間的那部分輸入電壓的一半這里輸入一半是什么意思? 還有通訊芯片datasheet里參數(shù) 提到驅動共模輸出電壓 在實際的應用中 這參數(shù)怎么用

2015-02-04 16:37:01

許多的資料顯示,許多的EMC問題都是由共模及差模干擾引起的,那么在單板調試過程中,有沒有什么好的辦法對電路板上的共模和差模電壓進行測量,測量用的儀器比如示波器,測量方法什么的。請各位大佬賜教

2018-05-27 14:58:57

之間。盡管雙電源供電時沒有地平面與運放相連接,我們可以把共模電容看作與負電源端相連,交流等效到地。在需要關注穩(wěn)定性的高頻區(qū)域,運放的開環(huán)增益低,在兩個輸入端之間實際上存在一個交流電壓。這將導致差模電容

2018-09-21 15:29:00

其他入口點中的交流電源耦合,如Ce1和Ce2等。儀表放大器儀表放大器的電源電壓必須足夠高,以便支持通常為±1.0 V的差分和共模輸入電壓范圍。某些應用需要更高的差分輸入電平:±2.0 V。儀表放大器

2018-10-18 11:19:15

共模扼流圈 (Common Mode Choke),也叫共模電感,是在一個閉合磁環(huán)上對稱繞制方向相反、匝數(shù)相同的線圈。常用于過濾共模的電磁干擾,抑制高速信號線產(chǎn)生的電磁波向外輻射發(fā)射,提高系統(tǒng)的EMC,在實際應用中一般是在差分的信號線上加共模電感。

2019-05-22 06:27:57

。內部共模反饋環(huán)路迫使VO U T, cm等于輸入端VOCM的電壓,從而達到完美的輸出平衡。將輸入端接到ADC驅動器處理高速信號的系統(tǒng)經(jīng)常會用到ADC驅動器。分隔距離超 過信號波長一小段的器件之間必須

2018-10-17 10:52:42

的共模電壓,并產(chǎn)生集中在 2.5V 的輸出電壓,以利用模數(shù)轉換器 (ADC) 進行采樣。通過使用不同的精度參考,可以輕松更改輸出共模。主要特色帶寬 > 15MHz轉換電流到電壓高側電壓范圍:5V 至 30V靈活的輸出共模電壓

2018-10-10 09:26:42

高速,高共模比的IPM接口專用光耦

2012-08-20 10:50:02

問題?

我的理解:

輸入的直流電壓信號應該在0-90mv內變化,輸出都應該成線性變化。(理解有誤?)正確的電路應該怎樣?

我用ADI公司的仿真軟件模擬過,如果共模電壓在2V左右或者接正負5V供電,(0-88mv)上述電路基本沒問題。如果不采用正負電壓供電,怎么樣在輸入端產(chǎn)生一個2V的共模電壓?

期盼解答!

2023-11-28 07:54:59

AD7795輸入端能承受的最大共模電壓

2023-12-15 07:53:25

你好,我是從事IC測試的,目前在測試AD8138,其中差分輸入失調電壓這個參數(shù),產(chǎn)品手冊給的信息是它等于二分之一的差模輸出電壓,即,Vosdm=1/2 Vodm。而共模輸入失調電壓等于共模輸出電壓

2023-11-17 16:13:48

描述的與該引腳上的電壓差不多,而是始終是750mV,也就是說無法讓輸出共模電壓為0.請問:這是什么原因造成的?我該如何更改電路能夠設置共模電壓為0V?2.調試過程中發(fā)現(xiàn),對于單極性的信號或者說只有正值

2018-11-12 09:41:19

我在設計用AD8139作為AD7626的驅動器,AD8139和AD7626均是單電源+5V供電,AD8139單端轉差分方式(AD8139反相輸入端接地或固定電壓),被采集信號電壓范圍0~4.8V

2018-09-17 15:24:39

我用FPGA跟一個ADC通過LVDS進行通信,F(xiàn)PGA規(guī)定用LVDS時,相應BANK的電壓為2.5V,這樣出來的LVDS信號的共模電壓在1.2V左右,而ADC使用的電源是1.8V,出來的L號共模電壓

2019-03-01 15:43:37

HMC960芯片應用時,采用阻容耦合,CMI(輸入共模電壓)、CMO(輸出共模電壓)必須連接嗎?

2023-11-15 07:05:33

LT1395運放的共模輸入電壓范圍是多少?輸入共模電壓和電源電壓之間的關系是怎樣的。數(shù)據(jù)手冊只給出了5V和±5V條件下的輸入共模電壓范圍。假如采用Vs=+7V單端供電,輸入共模電壓范圍是多少?

同樣運放輸出電壓和電源電壓的關系呢?

想用這款芯片做電壓跟隨,有沒有推薦的資料呢?謝謝!

2023-12-05 06:29:47

絕對輸入電壓范圍的干擾信號,信號鏈設計人員可能需要考慮儀表放大器,以在信號到達ADC前消除較大的共模。有三種偽差分配置:單極性、偽雙極性及真雙極性。ADI SAR ADC產(chǎn)品組合提供采用以上每一種配置

2018-10-18 11:25:47

對于具有差分輸入的開關電容 ADC,只要輸入電壓在 GND/VDDA 范圍內,我預計共模電壓不會受到限制。然而,STM32 ADC 僅允許 (Vref-VDDa) /2 左右的小范圍共模電壓。在某些

2022-12-14 06:13:56

STM32的ADC 電壓輸入范圍為: VREF- ≤ VIN ≤ VREF+。一般設計的時候會把VREF-和地相連, VREF+和VDDA相連。若MCU供電電壓為3.3V,則ADC輸入電壓范圍為0

2021-08-04 06:47:56

VIN一樣,用作另一個輸入。所選電阻值應滿足下式:通過疊加,當VIN為0時,輸出值與VOCM相同。由于VOCM是設置輸出共模的值,因此差分輸出為0。若R1 = RG且R2 = RF,則輸出電壓由下式

2019-09-29 08:30:00

與正滿量程(由基準電壓輸入設置)之間擺動。由于差分器件每一側180°反相,輸入共模固定。與偽差分器件相似,差分反相器件可限制其容許共模輸入范圍。此范圍可在產(chǎn)品數(shù)據(jù)手冊的規(guī)格表中找到。如下圖7所示。對于

2018-10-17 10:24:38

什么是共模與差模共模干擾產(chǎn)生原因共模干擾電流如何識別共模干擾 如何抑制共模干擾

2021-02-24 06:43:19

得放大器的輸出端和ADC的輸入端之間共模簡單對齊,兩者均需在AIN+和AIN?保持+0.525 V。同樣,注意幾個接地使能的放大器引腳功能(VSS),單電源現(xiàn)強制 設置為?2 V供電(新VSS)。CM電壓

2018-10-11 10:34:45

儀表放大器AD620的共模輸入范圍超過電源電壓,會影響共模抑制比嗎?比如AD620采用正負5V電源供電,放大倍數(shù)為10倍,測試時共模輸入范圍為7.07V / 100Hz,會影響共模抑制比嗎?

2023-11-15 06:49:17

我現(xiàn)在傳感器的共模電壓是4V左右,5V供電,靈敏度5mV/,但是芯片那邊輸入共模電壓范圍是2.5V左右,怎么解決,可不可以在輸入端加一個電阻分掉一部分電壓 然后交給后端處理?各位高手,謝謝啦

2013-10-18 11:52:53

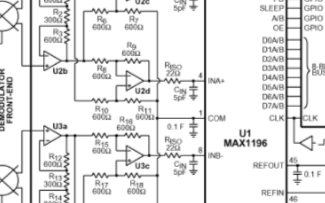

電路是高速FET輸入,增益為-5的儀表放大器(儀表放大器),具有寬帶寬(35 MHz)和出色的交流共模抑制CMR(10 MHz時為55 dB)。該電路非常適用于需要高輸入阻抗,快速儀表放大器的應用,包括RF,視頻,光信號檢測和高速儀器。高CMR和帶寬也使其成為寬帶差分線路接收器的理想選擇

2020-06-04 14:22:34

`為自己的電路挑選運放要通過一個選擇過程,其中要考慮到最關鍵的應用參數(shù)。審查的參數(shù)可能包括:電源電壓、增益帶寬積、轉換速率,以及輸入噪聲電壓。另外還必須考慮輸入共模區(qū)間,這對所有運放電路都是一個關鍵

2011-10-24 21:06:52

AD7760 datasheet里似乎沒有明確的說明內置運放輸入(VinA+/VinA-)的允許共模電壓范圍,圖52的例子里給的是共模電壓0V,輸入±2.5V的信號。

如果我希望在VinA+

2023-12-04 06:32:39

hi,我在研究ADL5566參數(shù)的時候,從手冊中了解到ADL5566的輸入共模電壓1.2V-1.8V/3.3VCC,但是我在看到ADL5566的demo板的時候,模擬輸入前端使用AC耦合,進入運放

2018-08-02 10:20:02

。這些電阻均采用相同的低漂移薄膜材料制成,因此在一定溫度范圍內可提供出色的比例匹配。ADC可采用5V單電源供電,參考引腳上有2.5V低阻抗電壓源。這樣可將輸出設為中間電源,并升高ADC輸入端呈現(xiàn)的共模電壓

2018-10-19 10:30:35

同相比例運算電路中,為什么運放的共模輸入電壓等于輸入電壓?還有,共模輸入電壓和輸入電壓分別指的是什么?共模輸入電壓應該是(uP-uN)吧,根據(jù)虛短原理這應該等于0吧,(P和N是下標)感覺不對,不曉得我哪里理解錯了,請大神賜教

2023-03-16 10:26:30

的電壓降低了,使得CCD 驅動器的自身功耗大幅度下降。由于共模扼流圈的差模電感很小,可以有效避免和CCD 的容性負載產(chǎn)生諧振,因此可以保證驅動信號的質量。 1 CCD驅動電路分析 為了設計高速

2018-09-28 10:11:39

正在做一個電壓采集的項目,輸入信號的共模信號,而28377S,16位ADC需要輸入差分信號,我利用下圖的方式將共模信號轉換成差分信號,請教TI工程師,能否這樣做。輸入的共模信號是0—2.5V的直流信號,在輸入之前已經(jīng)做了濾波處理。ADC的采樣時間是320ns,ADC時鐘頻率是40M。

2020-07-24 12:21:54

共模抑制和差模信號介紹不同結構的儀表放大器解析

2021-04-07 06:04:27

公司產(chǎn)品需要用到電流檢測,使用的是AD620,正負15V供電,原設計的IN+和IN-的最大共模輸入電壓為12V,所以AD620可以正常工作。 現(xiàn)在要做一款新的基板,也要用到儀表放大器,但其

2018-11-12 15:10:21

共模電壓,使共模電壓在測試的范圍之內,使采集芯片正輸入通道和負輸入通道(比如輸入通道AIN1+和AIN1-)各自的絕對電壓都在采集芯片允許的絕對電壓范圍之內,注意不是正輸入通道和負輸入通道的電壓差。請

2012-01-16 11:40:18

書上說相位,大小相同電壓叫作共模電壓,但我不明白共模輸入為什么是uic=1/2(ui1+ui2),我認為它應該跟差模計算方式一樣才對,共模輸入電壓我覺得應該是零才對啊,被共模電壓弄糊涂了啊~~~~~

2024-02-22 06:17:21

端(如果這代表了ADC或RLD基準電壓的中間值),并且將設備設置為顯示導聯(lián)II。導聯(lián)II顯示的電壓為VOUT,施加的電壓為VIN。 另一種測量共模抑制的方法是將所有電極連在一起,相對于大地驅動這些電極

2018-10-22 10:36:33

滿足最差情況交流電源輸入范圍要求。例如,澳大利亞西部的交流主電源電壓可高達264 VAC rms, 尖峰電壓達6 kV。在這種環(huán)境中,共模抑制必須比在美國(交流電源電壓為120 VAC rms)高出大約

2018-10-22 09:18:13

請問大佬怎么實現(xiàn)放大器與ADC之間的共模融合?

2021-04-13 06:33:06

怎么計算共模電壓大小

2023-11-27 12:43:45

專注于重要的信號...比賽。信號通過量及中斷我看比賽的程度類似于放大器CMRR。在真正談論CMRR之前,必須先談論共模電壓。對于非反相配置的放大器,輸入信號是共模信號。反相配置始終具有與輸入信號無關

2019-03-20 06:45:09

用數(shù)據(jù)采集卡測試SAR ADC/DAC,數(shù)據(jù)采集卡輸出和輸入(單端)的電壓范圍是-2V-2V,SAR ADC/DAC的輸入和輸出(單端)電壓范圍是0-2.5V,想用一個帶輸出共模電壓管腳的單端運算放大器匹配數(shù)據(jù)采集卡和SAR ADC/DAC之間的電壓范圍,求推薦,謝謝。

2023-11-15 06:37:35

求微弱電流檢測用的共模電壓范圍最大值大于65V的運算放大器或儀表放大器

2023-11-14 07:21:08

如圖2是運放TLC2272的共模輸入電壓范圍,圖5是其輸入電壓范圍,圖1是其仿真圖(信號源是300hz,Vp-p=5V,DC偏置為2.5V的正弦波;VCC=5V單電源供電,接成電壓跟隨器)。我

2017-12-28 21:57:58

輸入范圍:器件(運放、儀放……)保持正常放大功能(保持一定共模抑制比CMRR)條件下允許的共模信號的范圍。顯然,不存在“某一端”上的共模電壓的問題。但“某一端”也一樣存在輸入電壓范圍問題。而且這個范圍

2018-03-12 13:24:07

。顯然,不存在“某一端”上的共模電壓的問題。但“某一端”也一樣存在輸入電壓范圍問題。而且這個范圍等于共模輸入電壓范圍。道理很簡單:運放正常工作時兩輸入端是虛短的,單端輸入電壓范圍與共模輸入電壓范圍

2018-01-09 09:00:50

我用16位的ADC的輸入短接到共模電平上, 把輸出數(shù)據(jù)直接分析,發(fā)現(xiàn)最小2位數(shù)一直在變,這兩位應該是噪聲吧,算下來大約是1.08mV.

改用電池供電以后,這個值也差不多.

請問底噪有這么大的噪聲么?都短路了.

一般的ADC能直接輸出幾位的精度呢?

2023-12-22 06:52:12

本文主要論述了輸入共模電壓范圍(Vcm)對于ADC的重要性。

2021-04-21 07:26:00

AD7403的規(guī)格書里只顯示了輸入電壓共模范圍的典型值是?200至+300 mV, 而沒有標注最大值和最小值。如圖。 我這邊使用發(fā)現(xiàn),輸入共模現(xiàn)在到2V的時候,還可以正常運行,所以有這個疑問。

2023-12-01 09:38:28

在閱讀AD8220的datasheet的時候,發(fā)現(xiàn)其中有對“共模輸入電壓與輸出電壓的關系”的描述。見下圖:這里的增益G為1,那么共模輸入為5.5V的時候,為什么輸出電壓是14.9V呢?請教各位,這張圖該如何理解?謝謝!

2018-11-22 09:42:25

[size=13.3333px]在AD9204的數(shù)據(jù)手冊中推薦使用全差分放大器ADA4938來作為輸入驅動,并且將ADC的Vcm輸出連接到ADA4938的共模設置引腳。[size=13.3333px

2019-02-22 13:09:48

AD7795輸入端能承受的最大共模電壓

2018-08-23 09:09:33

你好,我是從事IC測試的,目前在測試AD8138,其中差分輸入失調電壓這個參數(shù),產(chǎn)品手冊給的信息是它等于二分之一的差模輸出電壓,即,Vosdm=1/2 Vodm。而共模輸入失調電壓等于共模輸出電壓

2018-08-14 07:40:19

儀表yunrun.com.cn2、什么是共模干擾?共模干擾是指干擾電壓出現(xiàn)在儀表任一輸入端(正端或負端)對地之間的交流信號,這種干擾又稱為“對地干擾”和“縱向干擾”。 測量共模干擾電壓,可以用高阻電壓

2018-06-19 21:29:21

在看ADI問答中提到用儀表放大器參考點接地時,共模電壓是0.1V,想問怎么是得出的 ?為什么不是0V ?

2018-11-21 09:33:42

運放的單端輸入電壓范圍與共模輸入電壓范圍是一回事,怎么理解,沒看懂?對于其他放大器,怎么共模輸入電壓范圍就要小于單端輸入電壓范圍了

2019-06-11 04:36:19

運放共模輸入阻抗和差模輸入阻抗,這兩者有什么區(qū)別?

2021-03-29 07:55:35

運放輸入的共模信號和差摸信號,具體是怎么定義的?

2017-05-05 22:41:02

你好,我想咨詢下運放OP282的共模輸入電容和差模輸入電容是多少?在45度的相位裕度時帶寬是多少?謝謝

2023-11-23 07:23:24

是:反比例運放,反向端輸入Vi,則反向端的電壓為:Vi/2(共模)+Vi/2(差模)=Vi,正向端為:Vi/2(共模)+(-Vi/2)(差模)=0。所以說,"此放運放的共模信號將為0"

2018-01-31 21:34:00

=11.818181991577148px]輸出共模電壓范圍[size=11.818181991577148px]下圖1大致顯示了運算放大器輸入和輸出動態(tài)范圍的限制,與兩個供電軌有關。任何運算[size

2014-08-13 15:34:22

的電源系統(tǒng)電壓相差甚遠,當時通常為±15 V(共30 V)。 由于電壓降低,必須了解輸入和輸出電壓范圍的限制——尤其是在運算放大器選擇過程中。 輸出共模電壓范圍下圖1大致顯示了運算放大器輸入和輸出動態(tài)范圍

2018-09-21 14:50:51

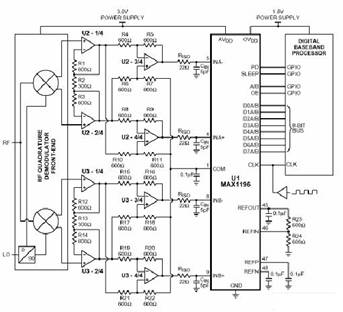

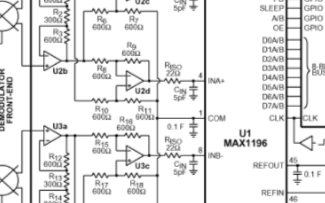

設置高速ADC的共模輸入電壓范圍--High-Speed ADC Sets Input Common-Mode Range

Abstract: The input common-mode

2009-06-09 20:41:43 1378

1378

運行典型高速ADC評估板設置

2013-08-22 16:35:05 24

24 輸入共模電壓范圍(Vcm)對于包含了基帶采樣和高速ADC的通信接收機設計非常重要,尤其是采用直流耦合輸入、單電源供電的低壓電路。對于單電源供電電路,饋送到放大器和ADC的輸入信號應該偏置在Vcm范圍以內的直流電平,能夠消除放大器和ADC設計的一大屏障,因為不必在0V保持低失真和高線性度。

2020-09-17 10:21:32 5716

5716

輸入共模電壓范圍(VCM)在包括基帶采樣高速ADC的通信接收器設計中非常重要。VCM對于具有直流耦合輸入的單電源低壓電路尤為重要。對于單電源電路,饋送驅動放大器和ADC的輸入信號應在VCM范圍

2023-02-25 12:10:09 789

789

輸入共模電壓范圍(VCM)在包括基帶采樣高速ADC的通信接收器設計中非常重要。VCM對于具有直流耦合輸入的單電源低壓電路尤為重要。對于單電源電路,饋送驅動放大器和ADC的輸入信號應在VCM范圍

2023-03-03 15:33:16 1652

1652

電子發(fā)燒友App

電子發(fā)燒友App

評論