本文介紹了基于FPGA、以并行多相濾波結構為算法基礎的超寬帶數字下變頻技術。設計過程包括高速AD信號降速預處理,應用SysGen開發環境完成的數字混頻、多相濾波和數據抽取,并通過仿真驗證了算法

2014-02-22 10:23:41 3144

3144 【作者】:張浩;張彧;潘長勇;【來源】:《電視技術》2010年02期【摘要】:實現了直接中頻采樣、數字下變頻的8PSK全數字解調,分析了數字下變頻、時鐘恢復、載波恢復等模塊的實現原理及方法。在

2010-04-23 11:16:42

問題,為什么不一次變頻到70M呢.我想用adf4153可以一次就產生1020-1820的混頻信號,為什么不這么做呢?問題二,是不是下變頻的主電路都必須做50歐的阻抗控制(非數字部分).第三,有沒有軟件可以對整個電路,包括adf4113,adf4153在內的下變頻,混頻,濾波,電阻橋負載均衡等進行整體仿真

2015-09-20 11:47:07

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字上下變頻的FPGA實現方法,以及Altera提供的一種數字信號處理的工具,DSP BUILDER。

2019-09-25 08:22:51

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。

2019-08-21 06:24:03

這是關于使用PXA的多載波GSM測量。在SWT / EVM菜單中,注意到“Carrier BPF Auto,Single and Multi”選項。你能解釋一下嗎?注意到在啟用此載波BPF的情況下

2019-05-30 12:54:44

多載波功率放大器測試系統

2019-07-16 11:22:37

現有的蜂窩基站大多采用超外差結構發送或接收射頻信號。這種結構需要兩次變頻或更多的上、下變頻級、中間濾波和模擬信號處理。圖1的上半部分給出了一個兩級轉換蜂窩基站的典型超外差發送框圖,很多此類發送器已經

2019-06-21 07:06:44

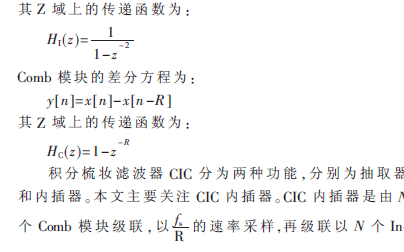

實現FPGA數字下變頻的多類濾波器分組級聯技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯并引入流水線技術以便于在FPGA上實現。數字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

AD采樣80MHz,中頻信號60MHz,在數字下變頻時NCO輸出頻率設置為多少?

2017-02-15 16:00:19

數字上/下變頻器:VersaCOMM?白皮書

2019-07-08 09:33:14

本帖最后由 eehome 于 2013-1-5 09:44 編輯

這是系統的一個模塊,實現了數字下變頻功能。

2012-06-06 15:59:13

。應用數字下變頻技術和Kay算法實現載波頻率的精確估計。設計實例的仿真結果表明了該環路的有效性,環路可在短對同內完成高精度的載波頻率同步。載波頻率同步在雷達和通信系統中得到廣泛應用。同步性能的好壞直接影響

2023-09-20 08:28:04

為什么調幅時增加調制信號的頻率會使調幅波的上下變頻的幅值減少?

2011-11-24 09:01:39

小弟最近在做一個數字下變頻和脈沖壓縮的仿真,現在一點頭緒都沒有,有沒有大神指教一下方向的。希望大神不吝賜教,或者是有源代碼能分享一下,跪謝了。

2017-03-11 10:50:24

近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(Digital Down Converter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分。基于FPGA的DDC

2019-10-12 08:17:00

基于FPGA設計了一高速數字下變頻系統,在設計中利用并行NCO和多相濾波相結合的方法有效的降低了數據的速率,以適合數字信號處理器件的工作頻率。

2019-09-26 07:06:35

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)設計高速的數據采集及正交下變頻系統,其中數據采樣速率90MSPS;實現70M中頻的數字正交下變頻…………請求大牛的幫助啊,我是小菜鳥,這方面還需要你們的大力提攜啊,萬分感謝

2014-04-01 10:44:33

對于在復雜的移動傳輸環境中傳送高速的數據流,小波包多載波調制通信系統在數據傳輸過程中仍然不可避免地存在著由于多徑效應引起的符號間干擾。在對多徑瑞利信道的建模基礎上分析了小波包多載波調制系統在瑞利信道

2010-05-06 09:03:24

數字上變頻/下變頻(DUC/DDC, digital up convert/ digital down convert)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率

2019-08-09 06:52:39

DUC/DDC的結構是怎樣構成的?DSP-BUILDER是什么?有什么功能?

2021-04-30 06:22:17

如何使用一個FPGA實現64個獨立的下變頻通道?

2021-04-29 06:37:05

求大佬分享利用FPGA技術實現的數字式頻分多路副載波解調器設計?

2021-04-08 06:52:08

如何去實現一種基于STM32的正弦波上下變頻呢?有哪些步驟?

2021-11-15 07:47:06

您好專家,有沒有關于多載波調制的文件?我無法理解附圖的測量結果,在我們的MCBTS測試中,有6個載波(間隔600khz),據我所知,應該有偏移600khz,1200khz,1800khz的載波功率

2019-05-14 09:51:27

針對頻分復用(FDM) 應用進行額外濾波。高性能GSPS ADC現將數字下變頻(DDC)功能在信號鏈中進一步提升,以使其位于基于賽靈思FPGA的設計解決方案的ADC之中。該方案為高速系統架構師提供了多種

2019-07-29 07:14:03

我是Xilinx的全新用戶,請耐心等待。我想實現數字下變頻器,但我需要的參數不同于ISE中提供的DUC / DDC編譯器。例如,我沒有使用特定的無線標準,我的通道帶寬是10 kHz而不是提供的選擇

2019-02-12 10:58:29

本文介紹了一種應用于數字化中頻頻譜分析儀的數字下變頻電路,整個電路基于FPGA實現,結構簡單,易于編程實現。

2021-04-15 06:21:22

RF:2.401GHz~2.473GHz IF: 中頻輸出大概在70M左右射頻輸入頻率范圍如上所示。求助下變頻芯片推薦

2012-03-14 19:01:37

賽靈思的FPGA在業內被廣泛應用于基帶協處理領域里的蜂窩射頻基站設計以及其它先進的基帶功能中。除了信道卡應用之外,賽靈思的FPGA還支持成本效益高的射頻卡功能的實現,如數字上變頻(DUC)和 數字下變頻(DDC),包括波峰因子降低(CFR)和數字預失真(DPD)等先進技術。

2019-08-14 06:28:54

簡要闡述數字下變頻器的發展和更新

2021-05-19 06:22:14

數字濾波器的實現一般有哪幾條途徑?寬帶無線通信的數字上下變頻是什么?濾波器的輸入數據流有什么特點?

2021-04-14 06:21:44

ad9361接收通道將信號通過正交調制下變頻變為I,Q兩路數據。信號傳播需要時間,這就造成了在接收端信號形式中有一個附加相位問題。就需要本振產生的載波同步。這里我有一個問題,就是本振產生的載波相位同步問題怎么解決?ad9361可以自動實現載波同步嗎,還是我通過FPGA自己處理,實現載波同步?

2018-08-22 09:02:46

GC5016及其結構是什么?怎樣去設計GC5016數字上下變頻系統的硬件部分?怎樣去設計GC5016數字上下變頻系統的軟件部分?

2021-05-24 06:49:59

本文介紹了數字下變頻的組成結構,并通過一個具體的實例,給出了FPGA 實現的具體過程。

2009-11-30 14:11:52 34

34 數字下變頻器中坐標變換模塊的ASIC 實現成都電子科技大學通信與信息工程學院劉欣 林水生 李廣軍摘要:本文介紹了一種基于CORDIC 算法的數字下頻器(DDC)中坐標變換模塊的

2009-12-24 10:54:50 13

13 WIMAX系統中的多天線技術及應用關鍵詞:wimax 天線摘要:本文介紹了WIMAX 系統中的多天線技術及應用WiMAX(全球互通微波接入)技術是以IEEE 802.16 系列標準為基礎的寬帶無線接

2010-01-27 14:28:39 31

31 FPGA在軟件無線電中的工程應用之數字上下變頻篇

2010-02-09 11:10:36 59

59 在微型SAR 實時成像樣機的設計中,對雷達回波在中頻進行采樣,然后采用數字下變頻技術實現正交解調,可以減少系統的復雜性,提高雷達的數字化程度和性能。該文針對微型SAR 方

2010-02-09 11:59:45 17

17 介紹了一種基于新型FPGA的高速數字下變頻的實現方法,它充分利用數字下變頻的優化算法以及FPGA領域的新技術,去除由于數據速率過高而造成的各種瓶頸,極大地減少了計算量和FPG

2010-07-02 16:49:24 21

21 基于時頻分析和多載波通信理論,建立了基于脈沖成型濾波的時頻局部化寬子帶多載波系統仿真模型,對各種同步偏差給系統帶來的影響進行了理論分析和性能仿真.仿真結果表明,系統

2010-09-23 11:45:38 0

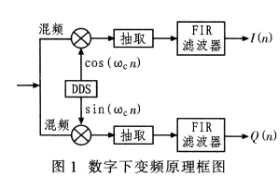

0 數字下變頻是軟件無線電系統的重要組成部分,主要完成對信號的混頻、濾波、抽取和整形等工作,包括數字混頻模塊和抽取濾波模塊。在數字下變頻系統實現方案中,輸入的模擬

2010-11-02 15:26:27 48

48 基于FPGA芯片Stratix II EP2S60F672C4設計了一個適用于寬帶數字接收機的帶寬可變的數字下變頻器(VB-DDC)。該VB-DDC結合傳統數字下變頻結構與多相濾波結構的優點,實現了對輸入中頻信

2010-11-11 15:56:54 57

57 數字下變頻器中坐標變換模塊的ASIC實現

1.引言 數字下變頻(DDC)技術是軟件無線電接收機的核心技術。其基本功能是從輸人的寬帶高速數字信

2007-08-15 16:32:54 1249

1249 WCDMA基站天線和多載波功率放大器方案

3G技術的應用推動了WCDMA在全球范圍內的競爭實力,在全球范圍商用程度逐漸成熟的過程中,產業鏈越趨完善、網絡建設覆蓋面積和業

2009-06-15 13:25:26 788

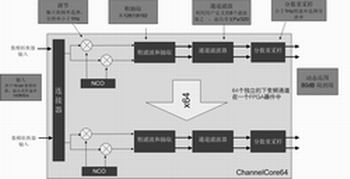

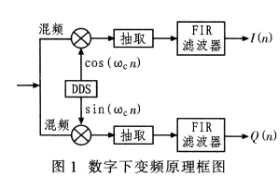

788 使用一個FPGA便可實現的64通道下變頻器

RF Engines公司的ChannelCore64使設計者能夠用一個可對FPGA編程的IP核來替代多達16個DDC(直接下變頻器)ASIC,可顯著減少PCB面積

2010-01-18 16:34:34 1147

1147

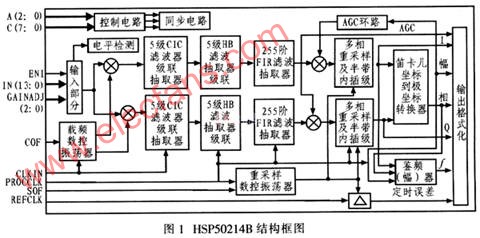

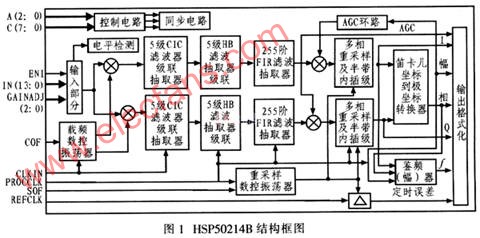

HSP50214B的內部結構HSP50214B型可編程數字下變頻器可進一步降低數字信號的載波頻率,甚至降到基帶;該器件可對輸入的數字信號進行抽取,在允許限度內降低數據量,利于后續

2010-08-11 09:18:17 1982

1982

數字下變頻是軟件無線電系統的重要組成部分,主要完成對信號的混頻、 濾波、抽取和整形等工作,包括數字混頻模塊和抽取濾波模塊。在數字下變頻系 統實現方案中,輸入的模擬中

2011-03-29 10:02:47 96

96 介紹了 多載波線性功放 的有關應用及技術,重點介紹了前饋線性功放和預失真技術。前饋功放是目前W-CDMA 多載波線性功放的主流技術,而基于數字信號處理的基帶預失真技術將會越來

2011-07-14 11:08:48 45

45 本文利用離散 小波包 變換導出信號空間的誘導小波包基。在此基礎上建立起基于DWPT的小波包多載波傳輸系統的概念,提出了最佳小波包多載波調制解調技術。該技術根據給定的信道特

2011-08-02 16:50:30 27

27 本文以某雷達對抗偵察數字接收機為例,介紹一種基于TI公司的DSP TMS320C6416的數字下變頻器。

2011-08-09 11:15:54 2425

2425

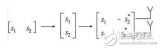

寬帶短波信道模擬器是一種運用仿真技術對真實的短波信道進行模擬的儀器。首先指出數字下變頻在寬帶短波信道模擬器中的作用。然后,闡述了數字下變頻中的數控振蕩器、CIC 濾波器

2011-09-15 18:30:21 1669

1669

闡述了雷達中頻正交采樣的原理,研究了使用System Generator實現數字下變頻的一種自頂向下的新型設計方法。在Simulink中進行了功能仿真驗證.

2012-02-09 15:13:48 46

46 結構類型的fir數字濾波器的fpga實現、不同結構fft的fpga實現、數字正交下變頻的fpga實現、cordic和dds的fpga實現等。

2015-12-23 11:07:46 44

44 基于半帶濾波器組的多載波多速率數字分路技術研究

2016-01-04 14:59:05 0

0 FPGA在軟件無線電中的工程應用之數字上下變頻篇

2016-04-25 09:38:10 8

8 基于FPGA的DDC數字下變頻設計,有興趣的同學可以下載學習

2016-04-27 16:18:12 59

59 一種基于流水線DA算法的數字下變頻器_周云

2017-01-07 22:14:03 2

2 數字下變頻程序,可直接用于項目

2017-08-30 08:45:24 23

23 針對軟件無線電接收機數字下變頻中高速數字信號的降采樣需求,利用半帶濾波器及級聯積分梳狀濾波器,設計了一種半帶濾波器前置的多級抽取濾波器架構。通過Simulink搭建系統模型驗證之后,利用Xilinx

2017-11-17 09:01:55 5303

5303 設計和實現了基于FPGA的可編程數字下變頻器(DDC),用于寬帶數字中頻軟件無線電接收機中,主要完成了數字下變頻、數據抽取等功能。采用自頂向下的模塊化設計方法,將整個下變頻器劃分為基本單元,實現這些

2017-11-22 09:09:56 5706

5706

介紹了幾種面向5G的新型多載波傳輸技術:濾波器組多載波(FBMC.Filter Bank Multicarri-er)、通用濾波多載波(UFMC,Universal Filtered

2017-11-22 11:04:35 17

17 數字下變頻是 無線通信 鏈路層的重要組成部分, 寬帶 信號和窄帶信號的下變頻由于信號帶寬不同而抽取因子不同,使得同時具有寬帶和窄帶信號的系統采用基于 FPGA 的系統很難實現。本文提出采用專用數字

2017-12-05 09:49:31 3044

3044

數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字上下變頻的FPGA實現方法,以及Altera提供的一種數字信號處理的工具,DSP BUILDER。

2019-03-13 15:16:58 1743

1743

帶有容限的載噪性能。本文將詳細介紹單載波及多載波WCDMA BTS中,對模擬正交調制器載噪比的相關技術要求。 在發射機系統中采用直接上變頻架構,通常被視為降低系統成本的方法,因為它可以降低系統復雜程度與組件數。圖1為WCDMA直接上變頻架構的結構圖。

2017-12-13 05:11:01 2991

2991

持MIMO(multiple input multiple output,多入多出)和自適應天線系統(adaptive antenna,system,AAS)兩種不同的多天線實現方式。MIMO是一種可選技術,在上下行鏈路都可以選擇支持。

2017-12-13 07:43:01 2838

2838

重新思考快速寬頻ADC中的數字下變頻

2018-04-23 10:41:12 1

1 CMY210是一個全端口、單端、通用上下變頻器。它結合了小的轉換損耗和優良的互調特性,低的LO和DC功率需求。

2018-07-27 11:30:00 15

15 數字上變頻/下變頻(DUC/DDC)是數字中頻設計的重要組成部分,其功能是將基帶信號經過內插濾波后變到中頻的頻率,或者將中頻的信號經過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數字

2018-09-15 04:57:00 2800

2800 軟件無線電的基本思想是把A/D變換器盡可能地靠近射頻天線,用軟件實現無線電系統的各種功能[1]。數字上變頻器是軟件無線電中發射機的核心部分,它的基本功能是增加基帶信號采樣率并將其上變頻到載波頻率

2020-01-29 17:29:00 3453

3453

整個軟件無線電系統的穩定性產生直接影響。采用專用DDC器件完成數字下變頻,雖具有抽取比大、性能穩定等優點,但價格昂貴,靈活性不強,不能充分體現軟件無線電的優勢。FPGA工藝發展迅速,處理能力大大

2020-08-06 15:31:17 728

728

本文檔的主要內容詳細介紹的是使用FPGA實現數字下變頻器DDC的設計資料合集免費下載。

2020-08-10 17:27:46 26

26 研究了高倍抽取的數字下變頻設計,重點分析了基于級聯積分梳狀濾波器和級聯半帶濾波器的多級抽樣頻率算法。并提出了用最新的Systemgenerator軟件實現FPGA 的設計、仿真方案,縮短了開發周期

2020-11-05 17:04:55 14

14 界。應用數字下變頻技術和Kay算法實現載波頻率的精確估計。設計實例的仿真結果表明了該環路的有效性,環路可在短對同內完成高精度的載波頻率同步。

2021-02-05 17:35:53 36

36 AN-807: 多載波WCDMA的可行性

2021-03-21 02:13:27 7

7 數字上/下變頻器簡介:VersaCOMM?可重構數字轉換器

2021-05-12 20:53:04 0

0 基于FPGA的DDC(數字下變頻)設計與實現(電源技術審稿費多少)-該文檔為基于FPGA的DDC(數字下變頻)設計與實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 12:04:22 28

28 基于FPGA的數字下變頻器(DDC)的設計(ups電源技術轉讓)-基于FPGA的數字下變頻器(DDC)的設計.適合新手學習參考

2021-09-16 11:43:52 37

37 該下變頻器提供兩種頻率轉換模式。該器件能夠從正交解調直接變頻為基帶IQ輸出信號,并從鏡像抑制下變頻為復中頻輸出載波頻率。

2022-11-14 16:26:27 414

414 然而,現有的設備大多是6GHz以下的設備,如何在已有設備的基礎上,滿足5G毫米波設計和開發的需求呢?虹科提出了經濟高效的5G毫米波擴展方案,能夠將現有的低于6GHz的設備經濟地擴展到5G毫米波頻段,并且能夠做到在升級到5G毫米波的同時降低成本和所需時間,輕松地實現上下變頻。

2022-11-16 14:19:25 2149

2149 在本文的第一部分“數字下變頻器——第1部分”中,我們探討了行業對更高頻率RF頻段采樣的推動,以及數字下變頻器(DDC)如何實現這種類型的無線電架構。討論了與AD9680系列產品中的DDC相關的幾個技術方面。

2023-01-05 14:28:21 1997

1997

電子發燒友網站提供《數字下變頻在人工智能引擎上的實現應用說明.pdf》資料免費下載

2023-09-13 15:06:31 0

0

電子發燒友App

電子發燒友App

評論