如果要將其錄音以數字形式的數據保存,則應將其模擬錄音信號變換成數字形式的數據,這就給原始數據的保存帶來諸多不便。因此,筆者按G.723標準設計了一種數字錄音機,它以ADSP-2181作為語音處理器和系統控制器,取消了普通錄音機的機械部分和磁帶,以大容量的閃速存儲器(Flash RAM)作為數字語音數據存儲器。該樣機體積很小,錄音時間長,沒有機械噪聲及機械故障,很有實用價值。

?

?

1 G.723標準簡介和系統結構框圖

1.1 G.723標準簡介

G.723是ITU-T在1996年制訂成型的一種多媒體語音編解碼標準。其典型應用包括IP電話服務、H.324視頻電話、無線電話、數字衛星系統、數電倍增設備(DCME)、公共交換電話網(PSTN)、ISDN及各種多媒體語音信息產品。G.723標準傳輸碼率有5.3kb/s和6.3kb/s兩種,在編程過程中可隨時切換。該標準主要包含了編碼算法和解碼算法。原理是:從采集的語音信號中解析出聲道模型參數,構造一個合成濾波器,采用合適的激勵源激勵,編碼傳輸的參數主要是激勵源與合成濾波器的參數。5.3kb/s的編碼器采用代數碼線預測激勵(ACELP);6.3kb/s的編碼器則采用多脈沖最大似然量化(MP-MLQ)激勵。根據傳輸編碼參數,可重構激勵源與合成濾波器進行解碼,還原出來的數字語音信號經D/A轉換器轉換成模擬語音信號。關于G.723的編碼和解碼的詳細說明見參考文獻[2]。?

G.723算法對語音信號有很好的編解碼效果,同時也可處理音樂和其它聲音信號,典型輸入是64kb/s(8k%26;#215;8)或128kb/s(8k%26;#215;16)的A律或μ律的PCM采樣語音信號。每次處理一幀語音信號,每幀240個采樣點(30ms)。在5.3kb/s的碼率下,每幀語音被壓縮成20個字節傳輸;在6.3kb/s的碼率下,每幀語音被壓縮成24個字節傳輸。

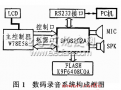

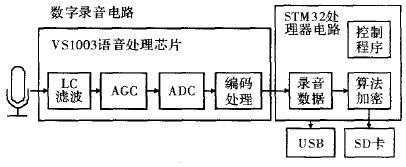

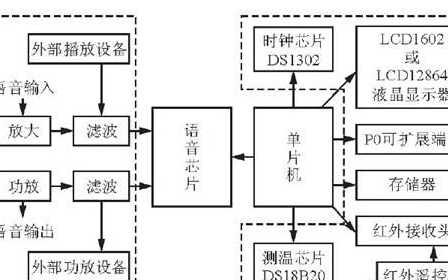

1.2 數字錄音系統的結構框圖

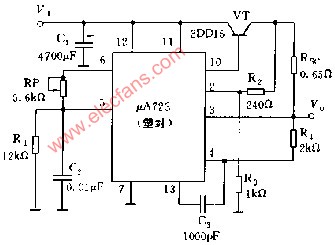

系統框圖主要由圖1所示的五部分組成。

?

AD73311用來進行A/D和D/A轉換,它集成了模/數和數/模轉換功能,而且可編程控制,使用極其方便;ADSP-2181為系統的核心數字處理器[3],時鐘頻率為33MHz,其功能強大;KM29N32000為閃速存儲器(Flash RAM),用來存儲已壓縮的語音數據;AT27C010(EPROM)用來存放控制ADSP-2181工作的程序;LCD用來顯示系統當前的工作狀態。系統的工作流程是:模擬語音信號經AD73311采樣并經A律或μ律壓縮后轉換成PCM數據,通過ADSP-2181的串行口送到ADSP-2181,ADSP-2181再將數據進行編碼和壓縮后送到閃速存儲器KM29N32000中存儲起來;錄音回放時,從KM29N32000讀取壓縮數據,送回ADSP-2181進行解碼,再送到AD73311進行D/A轉換,輸出模擬語音信號。整個過程都是由存放在AT27C010中的DSP程序控制,有條不絮地工作。LCD顯示系統當前的工作狀態。

2 系統各主要部分的原理與接口

2.1 AD73311與ADSP-2181的接口電路及編程控制

2.1.1 AD73311與ADSP-2181的接口電路

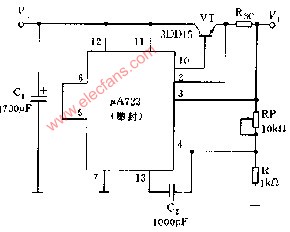

AD73311具有A/D和D/A轉換功能,采樣頻率為8kHz~64kHz,可以編程控制,采樣字長為16位。AD73311具有大信噪比、輸入輸出增益可編程控制、低工作電壓(2.7~5.5V),并且一片兩用的特點,是一種很受歡迎的芯片。AD73311與ADSP-2181的接口電路如圖2所示。 AD73311完成模擬語音信號的采集和數字語音信號的回放工作。從圖2中看出,信號從VIN處輸入,在VOUT處輸出回放語音信號。VIN處接麥克風,VOUT處接揚聲器。與ADSP-2181的通信通過串口進行,從SDO引腳向ADSP-2181輸出數據,從SDI引腳接收ADSP-2181數據,發送和接收可同時進行。時鐘信號由ADSP-2181的SLCK引腳接入。編程時必須先初始化AD73311的工作狀態,依次設定采樣率、輸入輸出增益、提前時間等,再讓其工作在數據傳輸模式下就可正常工作。AD73311進入數據傳輸模式后一直進行A/D或D/A轉換。在編程控制中,應讓ADSP-2181的串口一直工作在接收中斷方式,這樣可使數據發送與接收的速率保持一致。要改變工作模式可將其RESET引腳置低,再置高,這樣就可重新設定了。

2.1.2 AD73311的編程

?

AD73311是一種可編程的數據轉換器,內含五個8位控制寄存器CRA~CRE,用于設定工作狀態,控制輸入輸出。AD73311通過串行口與處理器接口,傳送的是16位數據,有五種工作模式,分別為:程序模式、數據模式、混合模式、模擬環路模式、數字環路模式。其中前三種是正常的工作模式,后兩種是調試模式,僅在調試時使用。五種工作模式由內部的控制寄存器A中的四位(CRA0~3)控制。

程序模式:AD73311啟動或重置后即工作于程序模式,此時AD73311串行口輸入的數據將作為命令字以初始化內部控制寄存器組,之后AD73311根據初始化命令字進入相應的工作模式,在此之前AD73311串行口輸出的碼字是無效的。數據模式:此時AD73311串行口輸出的是A/D轉換的16位數據,輸入的是D/A轉換的16位數據。AD73311一旦進入數據模式,就不能再得到控制信息,所以就永遠處于這一模式,除非重啟動。這時硬件上可采用發送接收幀同步信號同步方式。混合模式:此時16位碼字可能是控制字,也可能是數據。碼字的最高位MSB用來標識這個碼字是控制命令字(MSB=1)還是數據(MSB=0,低15位是有效數據)。在混合模式下,ADSP-2181可以根據系統的運行狀況適時改變AD73311的工作參數,如放大器的放大倍數等。這時硬件上可采用發送接收幀同步信號異步方式,便于ADSP-2181的自主控制。

AD73311控制采樣率由時鐘分頻電路完成。時鐘分頻電路將從DMCLK引腳輸入的外部時鐘頻率MCLK通過主頻時鐘因子分頻為內部時鐘頻率DMCLK,MCLK有五種頻率選擇,由內部控制寄存器B中的CRB4~6三位控制。DMCLK決定了AD73311的采樣頻率,它也是AD73311串行口的幀同步頻率。DMCLK再經串行時鐘分頻因子分頻為串行時鐘頻率SCLK,DMCLK有四種選擇,由內部控制寄存器B中的GRG2~3兩位控制。?

?

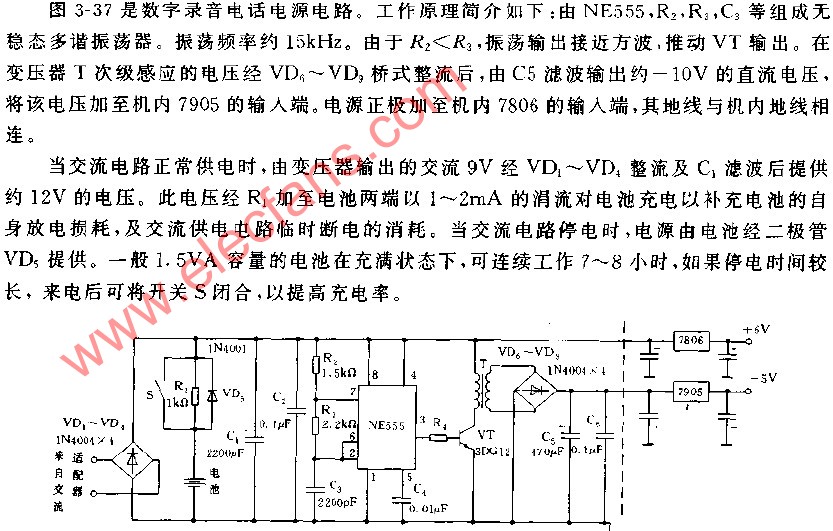

通過編程控制寄存器D,可控制輸入輸出的增益。輸入增益IG可在0~38dB之間調整,輸出增益OG可在-15~6dB之間調整。AD73311的具體編程流程圖如圖3所示,控制程序如下: AX0=DM(0x3fe5); {For 2181-PF0 connect with AD73311-RESET} AR=AX0 AND 0XFFFE; {PF0 pin reset} DM(0x3fe5)=AR; {RESET AD73311 to program} NOP; {Delay} NOP; NOP AX0=DM(0x3fe5); AR=AX0 or 0X0001; {2181-PF0 SET} DM(0x3fe5)=AR; {ready to program} ax0=0x82f9; {寫控制寄存器CRC,5V電源,使能ADC和DAC} tx0=ax0; IDLE; ax0=0x811b; {寫控制寄存器CRB,分頻,設置8K采樣率} tx0=ax0; IDLE; ax0=0x8320; {寫控制寄存器CRD,輸出輸入增益為0} tx0=ax0; IDLE; ax0=0x8400; {寫控制寄存器CRE,DAC延遲量為0} ax0=ax0; IDLE; ax0=0x8001; {寫控制寄存器CRA,進入數據傳輸模式} tx0=ax0; IDLE; 2.2 閃速存儲器與ADSP-2181的接口電路閃速存儲器采用韓國三星公司生產的KM29 N32000,容量為4M%26;#215;8=32Mbit,分成512塊,每塊有16頁,每頁528個字節。可進行100萬次擦寫,數據保存時間為10年,通過編程可自動進行擦寫。這里用于保存錄音數據,其數據保存不需要充電維持。?

從理論上說,如果采用G.723標準算法,在8kHz的采樣率下,采用5.3kb/s的碼率,錄音時間最大值約為100分鐘;在6.3kb/s碼率下最大錄音時間約為83分鐘,比常用的錄音磁帶略長,可以滿足般的錄音要求。如果采用KM29V64000(8M%26;#215;8=64M bit),錄音時間可增加一倍。如果需要更長的錄音時間,可選擇容量更大的閃速存儲器。有關KM29N3200的詳細特性見參考文獻[4]。

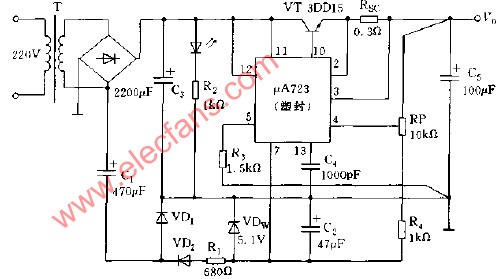

KM29N32000與ADSP-2181的接口電路如圖4所示,它的讀寫及擦除操作說明如下: (1)讀操作首先讓CLE置高,進入命令模式。此時ALE置低,從I/O口輸入00H(表示讀操作控制命令字),接下來CLE置低,ALE置高,進入地址加載模式,將要訪問的24位地址(A0~A23)分三次由低到高從I/O口磅入。適當延遲后,將ALE置低,就可連續地進行讀操作,每次讀取一幀數據。得到的數據是加載地址開始的。整個過程CE必須保持低電平。 (2)寫操作寫操作過程與讀操作類似,開始控制命令字是80H,將加載地十分三次送入后,適當延遲,就可連續地向閃速存儲器寫入一幀數據。數據寫完時,CLE置高,送入10H命令字,進行寫操作。 (3)擦除操作 保存數據時,如果對應存儲區已經有數據,就必須先擦除掉原來數據。每次擦除一次,每塊8K字節。首先輸入控制命令字60H,接著把塊地址分兩次送出,再輸入D0H命令字進行塊擦除。擦除完后,輸入命令字70H,可讀取擦除狀態。如果接下來讀取的數據的LSB位為"0"則表示擦除成功,為"1"則表示產生了錯誤,可重新進行擦除操作。如果再次錯誤,可能是對應單元出錯了。在訪問Flash RAM的內存操作中,最重要的是要注意各個信號的時序。必須嚴格按照說明書的時序圖進行操作才能實現正常的功能。

2.3 LCD顯示及接口電路

在本系統中用LCD顯示當前系統處于的狀態,如錄放狀態、進行的時間等。可由ADSP-2181進行控制,設定顯示方式及內容。所用的是點陣式液晶顯示器,為日立公司的HD44780A00LCD。里面有專用集成電路作為點陣的控制驅動,只要直接送入數據和指令就可實現所需的顯示。在本系統中,由于LCD使能信號脈寬較大,無法直接由DSP產生,因此通過觸發單穩觸發器74LS123來產生LCD使能信號。接口電路如圖5所示。通過調節連接74LS123的R和C值可控制輸出Q的脈寬tW。當C≥1000pF時為: tW=K%26;#183;R%26;#183;C 其中K為常數,與外界溫度及外接電容C有關,在0.2~0.6間選擇。 當C≤1000pF時,tW估計值如下: tW=6+0.05C(pF)+0.45R(kΩ)C+11.6R 當74LS123引腳A出現一個下降脈沖時,輸出Q產生一個高電平脈沖,脈寬由R和C決定,驅動LCD工作。錄音時LCD上面一行顯示RECORD,下行則顯示進行的時間;放音時上面一行顯示PLAY,下行也顯示進行的時間。時間的顯示通過ADSP-2181里面定時器中斷進行。

?

?

3 系統控制軟件設計

ADSP21XX系列提供了一整套軟件開發工具及相應的仿真器開發平臺,給系統的調試與仿真提供了極大的方便。軟件開發系統包括系統建造器、帶運行時時間庫的C編譯器、匯編器、連接器、PROM劃分器等。通過編譯連接匯編源程序,可以生成EXE文件。此文件是存儲映像文件,可以加載到仿真器上進行仿真;調試成功后,通過PROM劃分器和EPROM燒制設備可以寫入EPROM,系統復位時DSP加載EPROM程序便可自動運行,控制整個系統的工作。系統軟件設計采用自舉和中斷控制兩種方式。自舉方式系統一上電,ADSP-2181讀取EPROM中的程序,自動運行程序去控制整個系統工作。

中斷控制利用了ADSP-2181的兩個中斷,即sport0接收中斷和timer中斷。ADSP-2181的sport與AD73311相連。當得到一個采樣數據時,產生一個接收中斷,ADSP-2181讀取便得到采樣數據。由于sport0是全雙工的,當產生接收中斷時,同時可以發送數據,一方面在錄音時可以得到回放效果;另一方面則在播放時可直接發送數據,而對采樣數據置之不理,這樣便于解碼數據以固定的碼率回放。Timer中斷定時檢測外部控制引腳狀態,包括錄音、放音、快放及碼率轉換4個引腳,每個引腳的0/1狀態對應兩種控制,即開始錄音/停止錄音、開始放音/停止放音、5.3kbps/6.3kbps碼率轉換及快放狀態,共有七個狀態。 DSP匯編語言的結構與ASM匯編語言類似,其開頭部分對應中斷向量表。工作在中斷方式時,則向量表對應中斷處一般為一條跳轉語句;產生中斷時,則跳到相應語句執行中斷控制功能。主程序的中斷設置部分如下: JUMP start;NOP;NOP;NOP; {reset start interrupt} RTI;NOP;NOP;NOP; {IRQ2} RTI;NOP;NOP;NOP; {IRQL1} RTI;NOP;NOP;NOP; {sport0 transmit} JUMP sportReceive;NOP;NOP;NOP; {sport0 receive} RTI;NOP;NOP;NOP; {IRQE} RTI;NOP;NOP;NOP; {BDMA} RTI;NOP;NOP;NOP; {sport1 transmit} RTI;NOP;NOP;NOP; {sport1 receive} JUMP settimer;NOP;NOP;NOP; {timer interrupt} RTI;NOP;NOP;NOP; {PowerDown} sporto和timer中斷控制說明如下: (1)sporto接收數據中斷在程序中,數據處理集中在此進行。主要過程是:在錄音時,每收到240個采樣數據,就進行G.723編碼,將編碼結果保存到閃速存儲器中;在播放時,每次讀取24個數據,將讀取的數據進行解碼,再通過串行口發送出去,經揚聲器還原成語音信號。其流程如圖6所示。(2)timer中斷 timer中斷用來檢測用戶的控制信息及顯示運行時間信息。用戶控制有4個,即碼率選擇、錄音控制、放音控制及快退控制。對應這4個控制引腳,初始設定為輸入態,然后通過檢測各個引腳的電平設定工作態。其流程如圖7所示。

4 系統調試

系統調試要使用AD公司提供的ADSP21XX系列的整套軟件開發工具和仿真器。筆者使用ADSP-2181-EZ-ICE仿真器進行調試。仿真器上自帶33MHz的2181,調試支持20個斷點,可單步、設斷點和全速運行,可隨時觀察和修改寄存器和存儲單元的值。仿真器上提供了一個14針的仿真接口,仿真器通過此接口仿真控制目標系統。仿真器與計算機間有一個RS-232接口,通過數據進行連到計算機的串行口上,在仿真器開發平臺上就可以進行軟件調試。系統調試時遇到的主要問題是存儲器讀寫及LCD的顯示問題。開始時發現寫進閃速存儲器的數據與讀出的數據不符。經仔細分析,發現是由于沒有嚴格按照閃速存儲器的讀寫操作時序進行編程,或是延遲量不夠,或是兩個信號的先后次序弄反了,數據可能根本沒有寫進去,讀出的數據當然是錯的。在嚴格按照其說明書的時序進行編程控制后,數據的讀寫擦除操作完全正常。在播放錄音數據時,曾出現聲音跳變不連續的問題,經分析發現原因在于地址定位時出錯。因為對閃速存儲器擔任時每次讀寫都是一幀數據,而編解碼時一次操作的數據為20/24個字節,兩者長度不一樣,需要進行轉換操作。

本系統中ADSP-2181處理器的機器周期為30ns,經設定最大的等待周期為7機器周期后也才有240ns,而LCD的工作使能脈寬至少要300ns。因此在硬件上增加了一單穩延遲電路,這樣便解決了此問題。

?

電子發燒友App

電子發燒友App

評論