lvds接口標準:

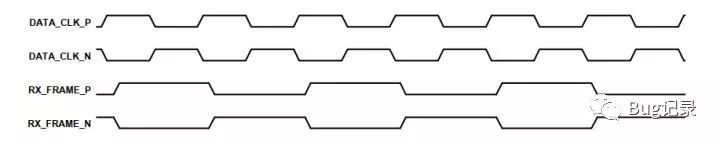

LVDS接口是LCD Panel通用的接口標準,以8-bit Panel為例,包括5組傳輸線,其中4組是數據線,代表Tx0+/Tx0-... Tx3+/Tx3-。還有一組是時鐘信號,代表TxC+/TxC-。相應的在Panel一端有5組接收線。如果是6-bit Panel則只有3組數據線和一組時鐘線。

LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也可以是平衡電纜。LVDS在對信號完整性、低抖動及共模特性要求較高的系統中得到了越來越廣泛的應用。目前,流行的LVDS技術規范有兩個標準:一個是TIA/EIA(電訊工業聯盟/電子工業聯盟)的ANSI/TIA/EIA-644標準,另一個是IEEE 1596.3標準。

1995年11月,以美國國家半導體公司為主推出了ANSI/TIA/EIA-644標準。1996年3月,IEEE公布了IEEE 1596.3標準。這兩個標準注重于對LVDS接口的電特性、互連與線路端接等方面的規范,對于生產工藝、傳輸介質和供電電壓等則沒有明確。LVDS可采用CMOS、GaAs或其他技術實現,其供電電壓可以從+5V到+3.3V,甚至更低;其傳輸介質可以是PCB連線,也可以是特制的電纜。標準推薦的最高數據傳輸速率是655Mbps,而理論上,在一個無衰耗的傳輸線上,LVDS的最高傳輸速率可達1.923Gbps。

---- OpenLDI標準在筆記本電腦中得到了廣泛的應用,絕大多數筆記本電腦的LCD顯示屏與主機板之間的連接接口都采用了OpenLDI標準。OpenLDI接口標準的基礎是低壓差分信號(Low Voltage Differential Signaling,LVDS)接口,它具有高效率、低功耗、高速、低成本、低雜波干擾、可支持較高分辨率等特點。LVDS接口在電信、通訊、消費類電子、汽車、醫療儀器中廣泛使用,并已經得到了AMP、3M、Samsung、Sharp、Silicon Graphics等公司的支持。為了向臺式機領域滲透,NS公司又專門針對LCD顯示器推出了新的支持OpenLDI標準的芯片組DS90C387和DS90CF388,新的芯片組支持從VGA(640×480)~QXGA(2048×1536)的分辨率。

---- DVI標準雖然還沒有OpenLDI標準那樣聲名顯赫,應用也沒有OpenLDI標準那樣普遍。但是由于有Intel、IBM、HP等大公司的加入,DVI的應用前景被普遍看好,一些數字型CRT顯示器、LCD顯示器和數據投影機中已經采用了符合DVI標準的數字顯示接口。

---- 目前大多數計算機與外部顯示設備之間都是通過模擬VGA接口連接,計算機內部以數字方式生成的顯示圖像信息,被顯卡中的D/A(數字/模擬)轉換器轉變為R、G、B三原色信號和行、場同步信號,信號通過電纜傳輸到顯示設備中。對于模擬顯示設備,如模擬CRT顯示器,信號被直接送到相應的處理電路,驅動控制顯像管生成圖像。而對于LCD、DLP等數字顯示設備,顯示設備中需配置相應的A/D(模擬/數字)轉換器,將模擬信號轉變為數字信號。在經過D/A和A/D2次轉換后,不可避免地造成了一些圖像細節的損失。

---- DVI標準由DDWG于1994年4月正式推出,它的基礎是Silicon Image公司的PanalLink接口技術,PanalLink接口技術采用的是最小化傳輸差分信號(Transition Minimized Differential Signaling,S)作為基本電氣連接。如附圖所示,計算機中生成的圖像信息傳送到顯示處理單元(顯卡)中,經處理并編碼成數據信號,數據信號中包含了一些像素信息、同步信息以及一些控制信息,信息通過3個通道輸出。同時還有一個通道用來傳送使發送和接收端同步的時鐘信號。每一個通道中數據以差分信號方式傳輸,因此每一個通道需要2根傳輸線。由于采用差分信號傳輸,數據發送和接收中識別的都是壓差信號,因此傳輸線纜長度對信號影響較小,可以實現遠距離的數據傳輸。在接收端對接收到的數據進行解碼,并處理生成圖像信息供數字顯示設備顯示。在DVI標準中對接口的物理方式、電氣指標、時鐘方式、編碼方式、傳輸方式、數據格式等進行了嚴格的定義和規范。對于數字顯示設備,由于沒有D/A和A/D轉換過程,避免了圖像細節的丟失,從而保證了計算機生成圖像的完整再現。在DVI接口標準中還增加了一個熱插拔監測信號,從而真正實現了即插即用

DVI標準一經推出立即得到了響應,不僅各圖形芯片廠商紛紛推出了系列支持DVI標準的芯片組,ViewSonic、Samsung等公司也相繼推出了采用DVI標準接口的數字型CRT顯示器和LCD顯示器。在新近上市的一些LCD和DLP數據投影機中我們也看到了DVI標準接口。隨著數字化時代的來臨,DVI標準接口取代VGA接口成為顯示設備事實標準接口指日可待。

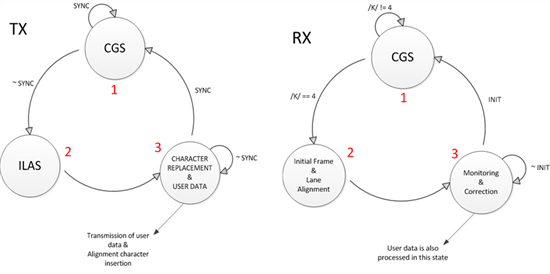

1 LVDS介紹

LVDS(Low Voltage Differential Signaling)是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

幾十年來,5V供電的使用簡化了不同技術和廠商邏輯電路之間的接口。然而,隨著集成電路的發展和對更高數據速率的要求,低壓供電成為急需。降低供電電壓不僅減少了高密度集成電路的功率消耗,而且減少了芯片內部的散熱,有助于提高集成度。

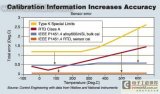

減少供電電壓和邏輯電壓擺幅的一個極好例子是低壓差分信號(LVDS)。LVDS物理接口使用1.2V偏置提供400mV擺幅的信號(使用差分信號的原因是噪聲以共模的方式在一對差分線上耦合出現,并在接收器中相減從而可消除噪聲)。LVDS驅動和接收器不依賴于特定的供電電壓,因此它很容易遷移到低壓供電的系統中去,而性能不變。作為比較,ECL和PECL技術依賴于供電電壓,ECL要求負的供電電壓,PECL參考正的供電電壓總線上電壓值(Vcc)而定。而GLVDS是一種發展中的標準尚未確定的新技術,使用500mV的供電電壓可提供250mV 的信號擺幅。不同低壓邏輯信號的差分電壓擺幅示于圖1。

LVDS在兩個標準中定義。IEEE P1596.3(1996年3月通過),主要面向SCI(Scalable Coherent Interface),定義了LVDS的電特性,還定義了SCI協議中包交換時的編碼;ANSI/EIA/EIA-644(1995年11月通過),主要定義了LVDS的電特性,并建議了655Mbps的最大速率和1.823Gbps的無失真媒質上的理論極限速率。在兩個標準中都指定了與物理媒質無關的特性,這意味著只要媒質在指定的噪聲邊緣和歪斜容忍范圍內發送信號到接收器,接口都能正常工作。 LVDS具有許多優點:①終端適配容易;②功耗低;③具有fail-safe特性確保可靠性;④低成本;⑤高速傳送。這些特性使得LVDS在計算機、通信設備、消費電子等方面得到了廣泛應用。

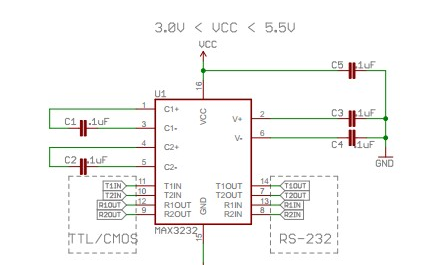

圖2給出了典型的LVDS接口,這是一種單工方式,必要時也可使用半雙工、多點配置方式,但一般在噪聲較小、距離較短的情況下才適用。每個點到點連接的差分對由一個驅動器、互連器和接收器組成。驅動器和接收器主要完成TTL信號和LVDS信號之間的轉換。互連器包含電纜、PCB上差分導線對以及匹配電阻。LVDS驅動器由一個驅動差分線對的電流源組成?通常電流為3.5mA),LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的電流大部分都流過100Ω?的匹配電阻,并在接收器的輸入端產生大約350mA 的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯″1″和邏輯″0″狀態。低擺幅驅動信號實現了高速操作并減小了功率消耗,差分信號提供了適當噪聲邊緣和功率消耗大幅減少的低壓擺幅。功率的大幅降低允許在單個集成電路上集成多個接口驅動器和接收器。這提高了PCB板的效能,減少了成本。

不管使用的LVDS傳輸媒質是PCB線對還是電纜,都必須采取措施防止信號在媒質終端發生反射,同時減少電磁干擾。LVDS要求使用一個與媒質相匹配的終端電阻(100±20Ω),該電阻終止了環流信號,應該將它盡可能靠近接收器輸入端放置。LVDS驅動器能以超過155.5Mbps的速度驅動雙絞線對,距離超過10m。對速度的實際限制是:①送到驅動器的TTL數據的速度;②媒質的帶寬性能。通常在驅動器側使用復用器、在接收器側使用解復用器來實現多個TTL信道和一個LVDS信道的復用轉換,以提高信號速率,降低功耗。并減少傳輸媒質和接口數,降低設備復雜性。

LVDS接收器可以承受至少±1V的驅動器與接收器之間的地的電壓變化。由于LVDS驅動器典型的偏置電壓為+1.2V,地的電壓變化、驅動器偏置電壓以及輕度耦合到的噪聲之和,在接收器的輸入端相對于接收器的地是共模電壓。這個共模范圍是:+0.2V~+2.2V。建議接收器的輸入電壓范圍為:0V~+2.4V。

2 LVDS系統的設計

LVDS系統的設計要求設計者應具備超高速單板設計的經驗并了解差分信號的理論。設計高速差分板并不很困難,下面將簡要介紹一下各注意點。

2.1 PCB板

? (A)至少使用4層PCB板(從頂層到底層):LVDS信號層、地層、電源層、TTL信號層;

(B)使TTL信號和LVDS信號相互隔離,否則TTL可能會耦合到LVDS線上,最好將TTL和LVDS信號放在由電源/地層隔離的不同層上;

(C)使LVDS驅動器和接收器盡可能地靠近連接器的LVDS端;

(D)使用分布式的多個電容來旁路LVDS設備,表面貼電容靠近電源/地層管腳放置;

(E)電源層和地層應使用粗線,不要使用50Ω布線規則;

(F)保持PCB地線層返回路徑寬而短;

(G)應該使用利用地層返回銅線(gu9ound return wire)的電纜連接兩個系統的地層;

(H) 使用多過孔(至少兩個)連接到電源層(線)和地層(線),表面貼電容可以直接焊接到過孔焊盤以減少線頭。

2.2 板上導線

(A) 微波傳輸線(microstrip)和帶狀線(stripline)都有較好性能;

(B) 微波傳輸線的優點:一般有更高的差分阻抗、不需要額外的過孔;

(C) 帶狀線在信號間提供了更好的屏蔽。

2.3 差分線

(A)使用與傳輸媒質的差分阻抗和終端電阻相匹配的受控阻抗線,并且使差分線對離開集成芯片后立刻盡可能地相互靠近(距離小于10mm),這樣能減少反射并能確保耦合到的噪聲為共模噪聲;

(B)使差分線對的長度相互匹配以減少信號扭曲,防止引起信號間的相位差而導致電磁輻射;

(C)不要僅僅依賴自動布線功能,而應仔細修改以實現差分阻抗匹配并實現差分線的隔離;

(D)盡量減少過孔和其它會引起線路不連續性的因素;

(E)避免將導致阻值不連續性的90°走線,使用圓弧或45°折線來代替;

(F)在差分線對內,兩條線之間的距離應盡可能短,以保持接收器的共模抑制能力。在印制板上,兩條差分線之間的距離應盡可能保持一致,以避免差分阻抗的不連續性。

2.4 終端

(A)使用終端電阻實現對差分傳輸線的最大匹配,阻值一般在90~130Ω之間,系統也需要此終端電阻來產生正常工作的差分電壓;

(B)最好使用精度1~2%的表面貼電阻跨接在差分線上,必要時也可使用兩個阻值各為50Ω的電阻,并在中間通過一個電容接地,以濾去共模噪聲。

2.5 未使用的管腳

所有未使用的LVDS接收器輸入管腳懸空,所有未使用的LVDS和TTL輸出管腳懸空,將未使用的TTL發送/驅動器輸入和控制/使能管腳接電源或地。

2.6 媒質(電纜和連接器)選擇

(A)使用受控阻抗媒質,差分阻抗約為100Ω,不會引入較大的阻抗不連續性;

(B)僅就減少噪聲和提高信號質量而言,平衡電纜(如雙絞線對)通常比非平衡電纜好;

(C)電纜長度小于0.5m時,大部分電纜都能有效工作,距離在0.5m~10m之間時,CAT 3(Categiory 3)雙絞線對電纜效果好、便宜并且容易買到,距離大于10m并且要求高速率時,建議使用CAT 5雙絞線對。

2.7 在噪聲環境中提高可靠性設計

LVDS 接收器在內部提供了可靠性線路,用以保護在接收器輸入懸空、接收器輸入短路以及接收器輸入匹配等情況下輸出可靠。但是,當驅動器三態或者接收器上的電纜沒有連接到驅動器上時,它并沒有提供在噪聲環境中的可靠性保證。在此情況下,電纜就變成了浮動的天線,如果電纜感應到的噪聲超過LVDS內部可靠性線路的容限時,接收器就會開關或振蕩。如果此種情況發生,建議使用平衡或屏蔽電纜。另外,也可以外加電阻來提高噪聲容限,如圖3所示。 圖中R1、R3是可選的外接電阻,用來提高噪聲容限,R2≈100Ω。

當然,如果使用內嵌在芯片中的LVDS收發器,由于一般都有控制收發器是否工作的機制,因而這種懸置不會影響系統。

3 應用實例

LVDS技術目前在高速系統中應用的非常廣泛,本文給出一個簡單的例子來看一下具體的連線方式。加拿大PMC公司的DSLAM(數字用戶線接入模塊)方案中,利用LVDS技術實現點對點的單板互聯,系統結構可擴展性非常好,實現了線卡上的高集成度,并且完全能夠滿足業務分散、控制集中帶來的大量業務數據和控制流通信的要求。

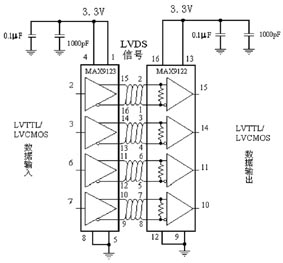

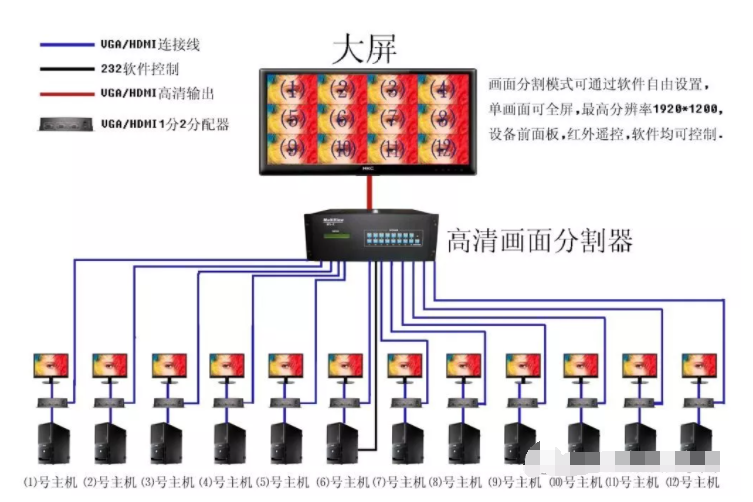

圖4描述了該系統線卡與線卡之間、線卡與背板之間的連線情形,使用的都是單工方式,所以需要兩對線來實現雙向通信。圖中示出了三種不同連接方式,從上到下分別為:存在對應連接芯片;跨機架時實現終端匹配;同層機框時實現終端匹配。在接收端串接一個變壓器可以減小干擾并避免LVDS驅動器和接收器地電位差較大的影響。LVDS接口定義。

電子發燒友App

電子發燒友App

評論