數字信號處理(Digital Signal Processing,簡稱DSP)是一門涉及許多學科而又廣泛應用于許多領域的新興學科。20世紀60年代以來,隨著計算機和信息技術的飛速發展,數字信號處理技術應運而生并得到迅速的發展。在過去的二十多年時間里,數字信號處理已經在通信等領域得到極為廣泛DSP技術圖解的應用。數字信號處理是利用計算機或專用處理設備,以數字形式對信號進行采集、變換、濾波、估值、增強、壓縮、識別等處理,以得到符合人們需要的信號形式。

本文為大家帶來基于DSP芯片的音頻信號濾波系統設計方案分享。

硬件設計方案

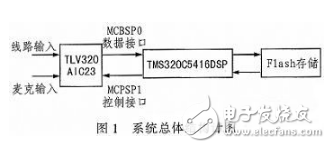

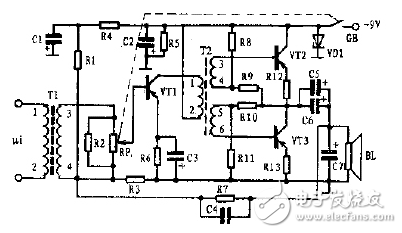

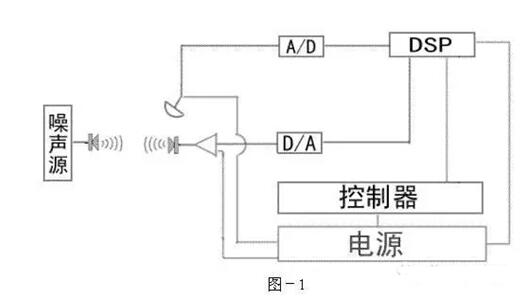

本系統采用DSP芯片TMS320C5416和TLV320AIC23音頻編解碼芯片實現系統的軟硬件設計,并在此基礎上完成語音信號的采集、播放、存儲、分析功能。文中包括3部分:音頻信號采集、DSP芯片處理信號、Flash存儲器。系統總體設計結構如圖1所示。

TMS320C5416是文中采用的主芯片,是一款低功耗、高性能的DSP芯片,主要功能包括采集語音信號、存儲以及控制模塊間通信等,將音頻信號經過采集和壓縮后存放到Flash存儲器中。AIC23的高性能立體聲信號的輸入支持MIC和LINE?IN兩種方式,可配置寄存器選擇,并且具有可編程增益調節。其內部集成模數和數模轉換部件,采用先進的采樣技術,采樣范圍在8K~96K之間。

本設計的從芯片TLV320AIC23音頻編解碼芯片,是立體聲音頻Codec芯片,主要負責對語音信號的A/D轉換,采樣編碼及濾波,該芯片是理想的音頻模擬器件,應用廣泛;DSP芯片三個中有兩個緩沖串口MCBSP0和MCBSP1負責控制音頻芯片AIC23,其中MCBSP0串口是SPI接口,實現語音數據的發送和接收,MCBSP1串口是I2S接口,任務是寫控制字;Flash存儲模塊可快速訪問可電擦寫,即使停電信息也不會丟失數據的存儲器,而且成本很低,可靠性高、穩定性強,容量大有幾GB,外形小巧等特性,進行讀取和存儲操作為載體。

?系統硬件電路設計

本系統采用的DSP芯片TMS320C5416,最高頻率可達160MIPS,系統實時性良好;音頻編解碼芯片TLV320AIC23采樣精度在16~32位。上述兩種芯片的結合是解決移動音頻錄放系統、現場采集語音的理想設計。TMS320C5416的3個MCBSP可以方便地實現 AIC23之間的控制和通信。AIC23是可編程芯片,其內部含有11個16位寄存器,由MODE引腳選擇控制接口采用SPI或者I2C哪種工作方式,MODE=0采用I2C模式;MODE=1表示采用SPI模式。

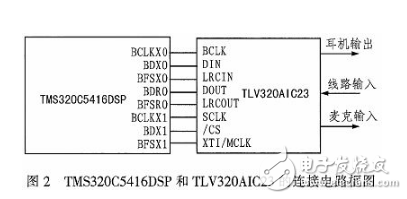

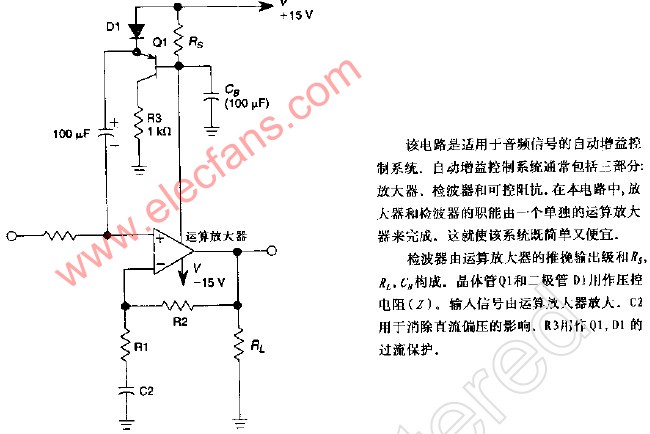

AIC23獨立的控制口接收控制器的命令字,而獨立的數據接口交換DSP語音數據。為DSP提供工作時鐘的是12M外部晶振。本系統C5416DSP的MCBSP0連接AIC23的控制接口,MCBS P1連接AIC23的數據接口。TMS320C5416DSP連接TLV320AIC23的接口框圖如圖2。

TMS320C5416DSP模塊設計

本次設計采用TMS320C5416芯片,其內部128K*16的RAM,能有效提高系統的集成度和總體性能。另外它還有3個多通道緩沖串口,提供128個通道。C5416芯片的特點有:工作頻率可達160 MIPS;可以訪問的數據存儲空間64K、I/O空間64K。

TMS320C5416和TLV320AIC23連接的引腳如下:BCLKX0/1:傳輸時鐘信號,是多通道緩沖串行接口發送器的串行移位時鐘信號,復位時,默認為輸入。當OFF為低電平,BCLKX進入高組態;TMS320C5416連接FLASH器件時,DSP芯片每次采集32位的語音數據,依次從左聲道開始往右聲道寫入Flash器件進行存儲。

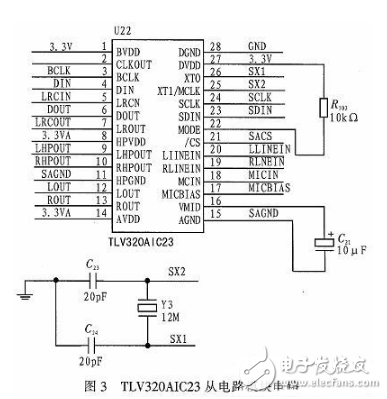

TLV320AIC23語音采集及回放接口電路模塊

AIC23芯片內部集成了ADC和DAC,兼容C5416的輸入/輸出電壓,它的數字接口和DSP的MCBSP端口無縫連接。AIC23采用先進的Sigma—delta過采樣技術,將大部分的噪聲轉移到阻態,采樣頻率范圍8K~96K提供4種16 bit、20 bit、24 bit和32 bit的采樣數據,ADC和DAC的輸出信噪比分別達到90 dB和100 dB。

TLV320AIC23與TMS320C5416連接的引腳圖如下。BCLK:I2S數字音頻接口時鐘信號,串行數據傳輸時鐘,當主模式是AIC23時,由AIC23產生BCLK且由它傳輸給DSP,此時的頻率僅為主時鐘的1/4,當從模式時,DSP產生BCLK;DIN:I2S格式輸入給D/A轉換器;DOUT,立體聲ADC產生,I2S格式A/D轉換器串行數據輸出:LRCIN/LRCOUT:I2SD/A和A/D轉換器字時鐘信號,主機模式下,AIC23產生該信號發送給DSP,從機模式下,由DSP產生;SCLK:控制端口串行時鐘輸入;SDIN:控制端口串行數據輸入,控制協議,傳輸配置數據;/CS:在SPI模式下,是數據鎖存控制端,在I2C模式下,作為外設7位地址的末位;XTI/MCLK:外部時鐘輸入。本文中AIC23由外接的晶振提供工作時鐘,TLV320AIC23從電路模塊電路如圖3。

語音數據存儲接口電路模塊

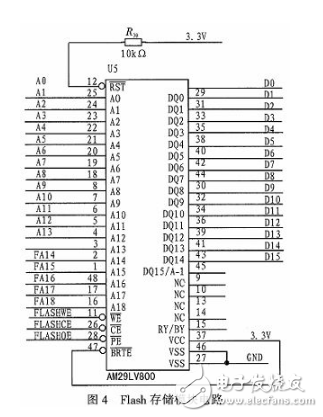

本文的語音數據存儲模塊采用32M*8位的Flash存儲空間,能夠滿足文中對存儲器芯片的容量以及讀取語音信號速度。Flash存儲器內存放錄音和放音系統數據。Flash的構成是由一組可獨立擦除的1KB區塊,擦除一個區塊將使該區塊全部復位為1。Flash存儲器每個區塊的基地址都固定不變。 Flash存儲器在存儲器中處于起始位置,一般從0開始。下圖4為Flash存儲模塊電路圖。

Flash存儲器是一種不揮發性內存,存儲特性相當于硬盤,因此成為便攜式數字設備的存儲介質,同時Flash存儲器采用串行結構,讀寫單元以頁和塊為單位,容量可以很大,成本低廉,而且又能確保數據讀寫的正確性。閃存的I/O端口有8位,數據傳送的方式是輪流傳送命令字。DSP采集到的32位語音數據,通過外部總線分4次,從左往右聲道寫入閃存中。

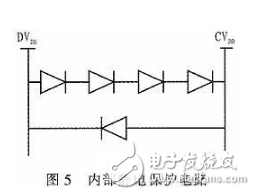

電源接口模塊

TMS320C5416DSP的供電結構采用雙電源器件芯片,內核電源CVDD和I/O電源DVDD,需要考慮相對電壓和上電次序。兩種供電控制策略不同:DVDD是3.3 V單電源上電,而CVDD只加載1.6 V,降低供電是想要降低芯片的功耗。雙供電模式可以消除電源間的延時。在理想狀態下,I/O電源和內核電源應該同時加電,但實際情況下想要做到并不容易。如果不能同時加電,需要根據引腳電平對工作模式進行配置,內核要優先于I/O供電,要求一種電壓要低于操作電壓,另一個電壓供電時間不能超出要求。上電過程中,要保證I/O緩沖接收到正確的內核輸出,并防止系統的總線沖突。加電次序主要取決于內部靜電保護電路如圖5所示。

圖中可見,需要DVDD不超出CVDD 2 V,于是采用4個二極管降壓,而內核電源不能超過I/O電源電壓0.5 V,因此只用一個二極管,否則容易損壞芯片。

系統軟件設計模塊

本語音錄放系統的軟件環境是DSP集成開發環境IDE提供成熟的核心功能和便捷的圖形可視化工具,使得設計更快。CCS2.0提采用圖形接口界面,有編輯工具和工程管理工具,提供軟件開發、程序調試和仿真環境,集成了匯編器、編譯器、建庫工具等。CCS集成的代碼調試工具具備各種調試功能,同時支持匯編和C/C++語言,本系統的程序軟件均采用C語言混合編寫。既容易調試,又能提高軟件的執行效率,能對DSP進行指令級仿真和實時數據分析。同時它還具有豐富的庫函數。

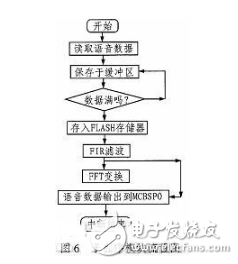

本系統的軟件部分主要是從現場線路輸入和麥克語音所采集到的信號,收集并存儲到Flash存儲器中,由濾波后播出信號,并將信號變換到頻域,即FFT離散傅立葉快速變換。

語音分析子模塊

現場輸入的語音信號,送入立體聲音頻編解碼器AIC23中,AIC23控制芯片內寄存器,將信號A/D轉換,用數字計算機處理數字信號,然后由數字濾波器濾波,再送到Flash存儲器暫存。數字濾波器是一個離散時間系統。程序語音模塊處理過程:首先初始化系統,包括設置時鐘發生器、AIC23的初始化、多通道緩沖、工作變量的初始等。

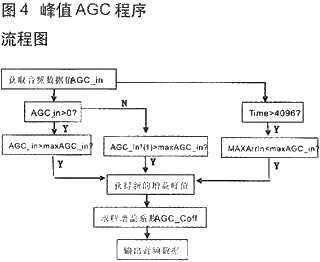

語音分析程序模塊處理過程:TLN320AIC23初始化,語音錄音數據讀取后存入數據緩沖區,調用FIR數字濾波器濾波,效果突出,然后將數字語音信號暫存在閃存內,最后由耳機發出,同時進行FFT離散快速變換算法。語音數據輸出到MCBSP。語音分析子程序模塊流程圖如圖6所示。

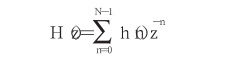

數字濾波器設計

使用窗函數的有限長,實現加窗線性相位FIR數字濾波器,能夠滿足轉移序列或脈沖響應的常見問題。

b=fir1(n,Wn,‘ftype’);

b=fr1(n,Wn,‘ftype’,‘window’);

n為濾波器的階數,Wn為截止頻率,ftype決定濾波器類型,high時為高通濾波器,stop時為帶阻濾波器。window采用窗函數類型,是一種通過截短和計權的方法使無限長非因果序列成為有限長脈沖應響應序列的設計方法,其默認值為漢明窗,w=hamming(n),產生一個n點的漢明窗函數。編寫matlab程序,生成FIR系數存放在FH[n]中,程序運行后在顯示區顯示結果。

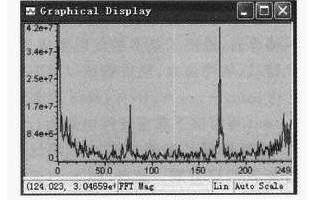

FFT是快速計算DFT的高效方法,能夠顯著降低運算量,大大提高DFT運算速度。大部分DSP芯片能在單指令周期內完成乘法累加運算。FFT算法是利用DFT系數的特性,合并運算,將長序列轉換為短序列DFT,以減少運算量。FFT算法的實現過程:

1)把N點的時域信號分解成N個時域信號,單點組成信號,并計算出頻譜。

2)輸入數據的比特反轉,即將輸入序列整理成位序顛倒的次序。位碼倒置可以提高程序執行速度和存儲效率。

3)實現N點復數FFT,執行3個循環套計算FFT變換,最內層都進行蝶形運算,第一級、第二級、第三級至第log2N級都是蝶形運算。序列點數N=2m,N為2的整數冪的FFT算法。

4)估計功率普

X(k)一般分成虛部和實部,計算時將FFT算法變換好的數據求平方和。

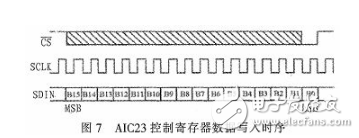

控制寄存器程序設計

本文的TLV320AIC23利用串行傳輸數據。前半部分數據控制所需存放寄存器地址,后半部分將所要寫入的值保存在寄存器中。采用兩個8 bit處理串行傳輸的控制數據。結合實際本文對于I2C寫入模塊采用匯編語言。

DSP通過I2C總線將配置命令發送到AIC23,完成初始化配置,然后AIC23開始工作。AIC23的初始化記錄在一個數組中,利用串口發送命令,采用循環方式發送。AIC23數據寫入時序圖如圖7。

如圖中所示B[15~9]是記錄控制寄存器的地址,B[8~0]是要寫入的值被保存在寄存器中。

電子發燒友App

電子發燒友App

評論