? | |

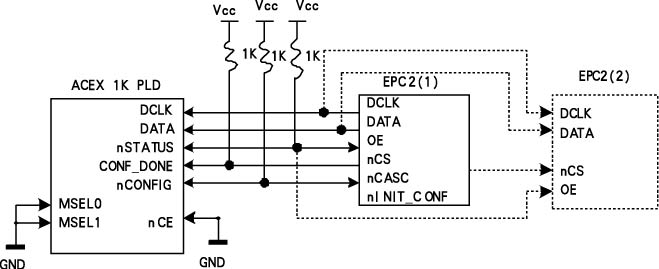

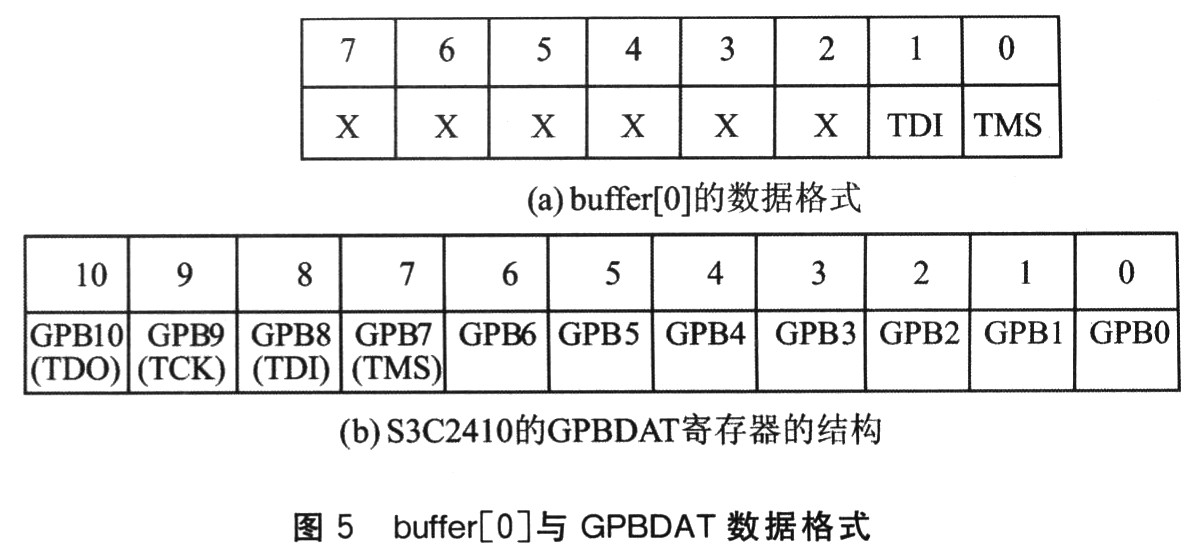

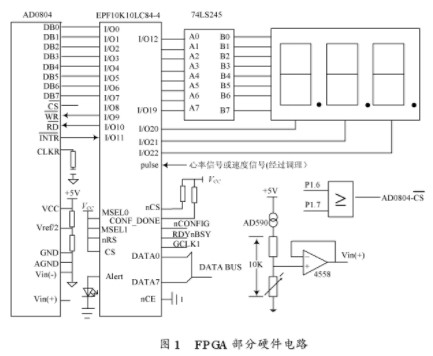

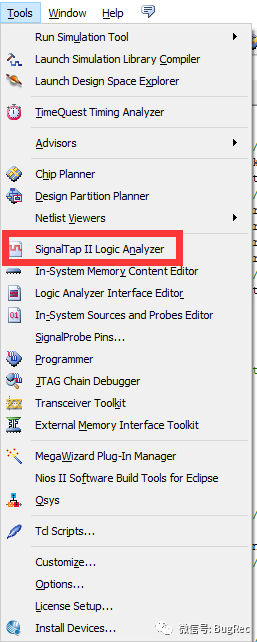

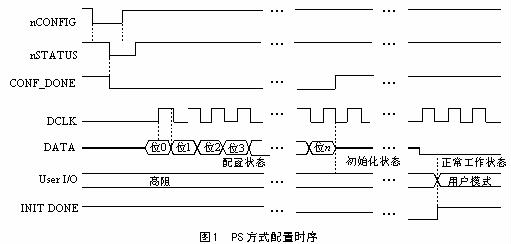

摘要:介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數據的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統的設計方法及實現多任務電路結構中配置的方法,并從系統的復雜度、可靠性和經濟性等方面進行比較和分析。 ? ??在當今變化的市場環境中,產品是否便于現場升級,是否便于靈活使用成為產品能否進入市場的關鍵因素。在這種背景下,Altera公司的基于SRAM LUT結構的FPGA器件得到了廣泛的應用。雖然這些器件應用廣泛,但由于其內部采用SRAM工藝,它的配置數據存儲在SRAM中。由于SRAM的易失性,每次系統上電時,必須重新配置數據,即ICR(In-Circuit Reconfigurability),只有在數據配置正確的情況下系統才能正常工作。在線配置方式一般有兩類:一是通過下載電纜由計算機直接對其進行配置,二是通過配置芯片對其進行配置。通過PC機對FPGA進行在系統重配置,雖然在調試時非常方便,但在應用現場是很不現實的。上電后,自動加載配置對FPGA應用來說是必需的。Altera公司提供的配置芯片有一次可編程型和可擦除編程型兩種:一次可編程型芯片只能寫入一次,不適合開發階段反復調試、修改及產品的方便升級;可擦除編程型價格昂貴,且容量有限,對容量較大的可編程邏輯器件,需要多片配置芯片組成菊花鏈形進行配置,增加系統設計的難度。 ? 為了降低成本,目前在開發階段多用可擦除型配置芯片;最終產品用不可擦寫的配置芯片,但一次簡單的代碼更換就需要更換一次器件,這在產品升級時很不實用。至今還沒有低成本的配置芯片出現,而我們采用的這套配置方案充分考慮了在FPGA實際使用中,對設計的保密性和設計的可升級的要求,不但可以實現代替價格昂貴的不可擦寫和可擦寫配置芯片,而且可以實現多任務電路結構重配置。該方案有PC機控制程序、單片機和外部串行存儲器組成,只要通過替換外部串行存儲器,就可實現對不同容量的多種配置芯片的代替。PC機是用來將配置數據寫入存儲器的,在寫好數據后該配置系統不再需要PC機的控制,在單片機的控制下實現ICR或多任務電路結構重配置。多任務電路結構重配置即將多個配置文件分區存儲到外部存儲器中,然后由單片機接收不同的命令,以選擇讀取不同存儲器區的數據下載到FPGA器件,實現在線配置成多種不同的工作模式。 ? 圖1 ? 1 FPGA器件的配置方式和配置文件 ? Altera公司生產的具有ICR功能的FPGA器件有FLEX6000、FLEX10K、APEX和ACEX等系列。它們的配置方式可分為PS(被動串行)、PPS(被動并行同步)、PPA(被動并行異步)、PSA(被動串行異步)和JTAG(Joint Test Action Group)等五種方式。這五種方式都能適用于單片機配置。PS方式因電路簡單,對配置時鐘的要求相對較低,而被廣泛應用。我們的配置方案也采用PS配置方式來實現ICR功能,圖1是PS配置方式的時序圖。 ? 被動串行工作過程:當nconfig產生下降沿脈沖時啟動配置過程,在dclk上升沿,將數據移入目標芯片。在配置過程中,系統需要實時監測,一旦出現錯誤,nSTATUS將被拉低,系統識別到這個信號后,立即重新啟動配置過程。配置數據全部正確地移入目標芯片內部后,CONF_DONE信號跳變為高,此后,DCLK必須提供幾個周期的時鐘(具體周期數與DCLK的頻率有關),確保目標芯片被正確初始化,進入用戶工作模式。 ? Altera的MAX+PLUS II或Quartus II開發工具可以生成多種配置或編譯文件,用于不同配置方法的配置系統,而對于不同系列的目標器件配置數據的大小也不同,配置文件的大小一般有.rbf文件決定。.rbf文件即二進制文件。該文件包括所有的配置數據,一個字節的 .rbf文件有8位配置數據,每一字節在配置時最低位最先被裝載。微處理器可以讀取這個二進制文件,并把它裝載到目標器件中。Altera提供的軟件工具不自動生成 .rbf文件,須按照下面的步驟生成:① 在MAX+PLUS II編譯狀態,選擇文件菜單的變換SRAM目標文件命令; ② 在變換SRAM目標文件對話框,指定要轉換的文件并且選擇輸出文件格式為 .rbf(Sequential),然后確定。 ? 2 配置電路結構和原理 ? ??? 2.1 串行通信的電路結構和原理 ? PC機與單片機的接口如圖2所示。AT89C2051單片機通過串行口直接接收PC機傳送來的串行數據,然后把接收到的數據存入數據存儲器。由于PC機的串行口都是RS-232C標準的接口,所以,其輸入輸出在電平上和采用TTL電平的AT89C2051在接口時會產生電平不同的問題。為了解決這個問題,在PC機和單片機的串行通信電路中加入了MAX232芯片,以實現TTL電平和RS-232C接口電平之間的轉換。這樣PC機和AT89C2051單片機進行串行通信時就可以順利進行了。除了電路結構之外,要實現PC機和AT89C2051之間的通信,還需要有合適的通信軟件。 ? ??? 2.2 ICR控制電路原理 ? ICR電路原理如圖3所示。AT24C256用來存儲FPGA的配置數據。 ? ICR控制電路的工作過程為:經MAXPLUS II編譯生產的配置文件(.sof)通過格式轉換成為 (.rbf)。然后,利用PC機端的控制程序,通過PC機的串行通信口,經U1存儲在U2中。U1再根據系統的要求,通過P1.2、P1.3、P1.4、P3.0和P3.1等5個I/O口,將其存儲在U2中的配置數據下載到電路中的FPGA器件中去。 ? 因作者設計電路中的FPGA是Altera公司的FLEX系列的EPF10K10,其配置文件的容量為15KB,故電路中采用1片AT24C128就可存儲EPF10K10的配置數據。我們選用AT24C256器件可以存儲兩個配置文件,是為了實現多任務電路重構,此時整個ICR控制電路只有2片IC。可以說,它是目前結構最簡單、成本最低的ICR控制電路。如果配置的FPGA是EPF10K30或更大門數的器件,則需要大容量的存儲器件或多片AT24C256。(在兩線串行總線上最多可接4片AT24C256。) ? 3 軟件設計 ? ? ??? 3.1 PC機端的軟件 ? PC機端的軟件采用Visual Basic語言編程。VB支持面向對象的程序設計,具有結構化的事件驅動編程模式,而且可以十分簡便地作出良好的人機界面。PC機端的控制程序主要實現讀取.rbf文件并將其通過串口送出的功能。讀取文件時,主要使用讀取二進制文件命令。在串口通信方面,使用VB提供的具有強大功能的串口通信控件MSCOMM。該控件可設置串口狀態及串口通信的信息格式和協議。 ? ??? 在實際工作中,要實現AT89C2051和PC機之間的有效通信,必須使其具有相同的波特率和相同的通信協議。作者采用了9600bps的波特率和N.8.1幀結構。N.8.1幀結構表示1幀串行數據有10位:起始位占用1位(低電平),用來表示字符開始;后8位為數據編碼,無奇偶校驗位;最后為停止位(高電平),用來表示字符傳送結束。單片機的串行口工作在方式1。方式1是標準的10位異步通信方式,10位數據和PC機的標準串口相對應,傳送的波特率由單片機工作時鐘和T1的溢出率共同決定。 ? ??? 3.2 ICR控制電路軟件 ? 在圖3介紹的ICR控制電路中,其存儲FPGA配置數據的存儲器 AT24C256采用I2C串行總線進行數據交換。其數據交換速度較慢,而FPGA配置數據又比較大,因此如何提高圖3介紹的ICR控制電路的配置速度將是軟件設計上的一個重點。限制速度的瓶頸主要是從AT24C256讀取數據和將數據寫入FPGA器件中。從AT24C256讀取數據,有讀當前地址、隨機讀和順序讀三種方式。這三種方式中,順序讀最簡單、速度最快。因為在同一片AT24C256中,僅需要寫入一次讀命令就可以按順序從0地址開始直至讀完整片AT24C256中的全部數據。向FPGA器件寫數據時,可以使用串行口的移位寄存器工作方式,即方式0。方式0數據的傳送以8位為1幀,無論是發送或是接收都是最低有效位居先。這和FPGA對數據的要求一致,傳送的波特率固定為振蕩頻率的1/12。本系統只需用到輸出方式,串行數據通過RXD端輸出,而用TXD端輸出移位脈沖。當1字節數據寫入串行數據緩沖器SBUF時,就開始發送。在此期間,發送控制器送出移位信號,使發送移位寄存器的內容右移1位,直至最高位(D7位)移出后,停止發送數據和移位時鐘脈沖。發送完1字節數據后,硬件置發送標志位TI為1,通過判斷TI的狀態決定是否向SBUF寫入數據。采用這種方式比采用普通(I/O)口要快很多。 ? 4 結 論 ? 我們設計的基于微控制器的FPGA器件的 ICR控制系統,具有線路結構簡單、開發容易、體積小、成本低的優點;可以支持3.3V和5V系統的配置;適用于需要ICR功能的電子裝置中。該ICR控制電路是為配置Altera公司FLEX系列的FPGA器件而設計的,稍加修改也適用于其它系列的FPGA器件。這個配置電路的主要弱點在于配置速率較慢,只能適用于配置速率要求不高的應用。

|

?

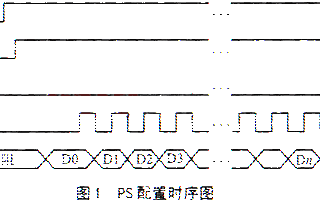

- FPGA(591967)

- 配置方法(7747)

相關推薦

FPGA芯片配置方式及常見配置方法

廣義的來說,FPGA的配置包括直接使用下載電纜對FPGA器件進行編程、對外部EEPROM和FLASH進行編程、使用MPU對FPGA器件進行編程、外部EEPROM和FLASH對器件進行編程等。

2016-10-26 10:58:27 9490

9490

9490

9490FPGA可重復配置和測試系統的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過將配

2011-10-12 15:16:25 1414

1414

1414

1414

遠程在線更新FPGA程序的方法

本文以提高FPGA遠程更新程序的方便性為目標,提出了一種基于EPCS Flash的遠程在線更新FPGA程序的方法,從而在應用中能夠使基于FPGA的產品更加方便地維護升級

2012-02-22 11:33:15 27516

27516

27516

27516

基于SPI FLASH的FPGA多重配置

通過FPGA的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPI FLASH為基礎,從硬件電路

2014-01-24 14:17:22 13669

13669

13669

13669

FPGA在線配置

FPGA在線配置連接好下載線,給SP6開發板供電。如圖所示,在“Design à Implementation”界面下,首先選中“Hierarchy”下的“sp6.v”文件,接著雙擊

2019-04-08 09:34:41

FPGA在線配置模塊和自動測試模塊實現過程

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過將

2020-05-14 07:00:00

FPGA配置電路

設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。(特權同學,版權所有)FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理如圖3.7所示

2019-01-30 02:34:52

FPGA配置問題

jtag調試時,fpga能識別到器件,但是下載程序失敗,針對這種情況,想問下各位:1、能識別到器件,說明fpga配置電路的哪些部分是正常的2、我描述的這種情況可能是由于什么原因導致的?

2014-05-04 10:50:29

FPGA中SPI復用配置的編程方法

FPGA中SPI復用配置的編程方法SPI(Serial Peripheral InteRFace,串行外圍設備接口)是一種高速、全 雙工、同步的通信總線,在芯片的引腳上只占用4根線,不僅節約了芯片

2012-08-12 11:56:42

FPGA中有哪些SPI復用配置的編程方法?

。正是出于這種簡單、易用的特性,現在越來越多的芯片集成了這種通信協議。FPGA中也有不少SPI復用配置的編程方法,但具體有哪些你們知道嗎?

2019-08-06 06:40:36

FPGA實戰演練邏輯篇13:配置電路

設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。(特權同學,版權所有)FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理如圖3.7所示

2015-04-13 12:29:55

FPGA實戰演練邏輯篇69:基于FPGA的在線系統調試概述

在線調試方式大都是通過FPGA器件引出的JTAG接口,同時使用了一些FPGA片內固有的邏輯、存儲器或布線資源就能夠實現的。這些調試功能通常也只需要隨著用戶設計所生產的配置文件一同下載到目標FPGA器件中

2015-09-02 18:39:49

FPGA的接口配置如何進行配置?

NOR閃存已作為FPGA(現場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數據吞吐量特性使得FPGA在工業、通信和汽車ADAS(高級駕駛輔助系統)等應用中得到廣泛采用。汽車場景中

2021-09-03 07:00:00

fpga 多配置的問題

請教一下各位,我那個fpga由于某個條件不能使用下載器固化程序,然后我現在使用上位機控制fpga把配置數據寫到flash里面去,這個方法有個問題就是在寫flash的過程中如果斷電,那原先flash

2019-11-05 08:53:55

Altium designer高版本如何在線搜索元器件

Altium designer高版本中可以在線搜索元器件,發現無法使用!方法是使用explorer有知道的么?

2018-02-01 12:52:55

Stratix V GX FPGA開發套件,配置問題求助

最近弄了個Stratix V GX FPGA開發套件,然后我看那個說明書,發現這個器件好像沒有配置芯片。。配置模式只有jtag,和fpp。然后以前自己的板子都是有jic文件下載到配置芯片里,這次

2014-11-20 15:58:02

Xilinx FPGA在線更新配置數據交流

我想要對FPGA實現脫離仿真器在線升級的功能,要能防掉電,不知道大家有做過的沒? 我現在的想法是通過外部cpu來對FPGA進行配置和升級,FPGA采用從模式,比如用一個DSP來配置FPGA,上電

2017-01-17 20:00:09

例說FPGA連載13:靈活定制——配置電路

。隨著芯片設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理如圖2.7所示。在FPGA

2016-07-27 16:45:59

例說FPGA連載18:配置電路設計

配置數據流從PC或者Flash存儲器中加載到FPGA內,使其運行起來。FPGA器件的下載配置,最常見的是基于JTAG的配置方式,這種方式既可以直接將PC上的配置數據流加載到FPGA上在線運行,也可以

2016-08-10 17:03:57

勇敢的芯伴你玩轉Altera FPGA連載14:FPGA下載配置電路

訪問端口和邊界掃描結構標準。隨著芯片設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。 FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理

2017-10-24 21:26:26

勇敢的芯伴你玩轉Altera FPGA連載52:Altera FPGA配置方式之AS/PS/JTAG配置方式

/s/1i5LMUUD AS配置方式由FPGA器件引導配置操作過程,它控制著外部存儲器及其初始化過程,EPCS系列配置芯片如EPCS1、EPCS4配置器件專供AS模式。使用Altera串行配置器件來完成

2018-03-05 16:30:35

如何使用高速NOR閃存配置FPGA

NOR閃存已作為FPGA(現場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數據吞吐量特性使得FPGA在工業、通信和汽車ADAS(高級駕駛輔助系統)等應用中得到廣泛采用。汽車場景中

2021-05-26 07:00:00

如何利用VC++程序設計FPGA重配置方案?

隨著大規模集成電路的快速發展,系統設計已從傳統的追求大規模、高密度逐漸轉向提高資源利用率,使有限的資源可以實現更大規模的邏輯設計。利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲

2019-08-07 06:17:30

支持重構的FPGA器件

近年來,隨著FPGA技術的發展,支持重構的FPGA器件新品迭現。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表結構。Xilinx支持模塊化動態部分重構的器件族有

2011-05-27 10:23:28

有什么FPGA可重構方法可以對EPCS在線編程?

的簡單操作來完成FPGA的工作方式重構,這種可重構方式結構簡單,配置靈活,用戶操作更加方便。本文首先介紹了FPGA常用的配置方式,然后詳細闡述了有什么FPGA可重構方法可以對EPCS在線編程?

2019-07-31 07:15:40

有什么好的FPGA在線培訓班嗎?

【FPGA入門教程】《HELLO FPGA》 - 項目實戰篇http://t.elecfans.com/981.html,重要的是免費在線學習。小梅哥FPGA設計思想與驗證方法視頻教程http

2018-09-11 09:38:25

玩轉Zynq連載5——基于Vivado的在線板級調試概述

FPGA片內固有的邏輯、存儲器或布線資源就能夠實現的。這些調試功能通常也只需要隨著用戶設計所生產的配置文件一同下載到目標FPGA器件中運行。相比于復雜的傳統臺式儀器,基于FPGA的在線調試僅需一條

2019-05-24 15:16:32

談談Altera FPGA的配置

不管Xilinx還是Altera,FPGA的配置模式或者方法多樣,尤其是Altera器件,什么AS模式、PS模式、FPP模式、AP模式等等。一般邏輯設計者可能不會關心到硬件的設計,但是FPGA的硬件

2015-01-28 10:27:03

可在線升級的FPGA并行配置方法的實現

針對基于SRAM 結構的FPGA,詳細介紹了一種采用可在線升級的SST89V564RD微處理器對其進行上電PPA(被動并行異步)配置,不僅實現了FPGA 的在線配置,而且通過微處理器的IAP 技術

2009-09-15 16:27:50 23

23

23

23FPGA器件在嵌入式系統中的配置方式的探討

通過說明FPGA 的各種配置方式及各種配置文件的使用,重點探討了在嵌入式系統中使用FPGA 的軟硬件設計。使用微處理器在線配置FPGA 時,需要將存儲在Flash 中的配置文件,通過微處

2009-09-16 10:52:02 10

10

10

10DSP和FPGA共用FLASH進行配置的方法

本文舉例分析了DSP的引導裝載過程和FPGA的配置流程,并據此提出了一種使用單個FLASH存儲器實現上述兩個功能的方法。

2010-07-21 17:14:42 12

12

12

12基于單片機的Cyclone系列FPGA配置方法

摘要:本文討論了Cyclone系列器件的不同配置方法,提出一種單片機結合FLASH存儲器的被動串行配置方案。關鍵詞:FPGA;FLASH;PS;Cyclone

2010-08-13 12:04:09 64

64

64

64基于ARM和FPGA的終端重配置硬件平臺實現

介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺設計方法。給出了系統設計的硬件結構和重要接口, 提出了由ARM微處理器通過JTAG在系統配置FPGA的方法, 以滿足重配置系統中軟件

2010-09-14 16:40:09 21

21

21

21FPGA的全局動態可重配置技術

FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54

54

54ACEX 1K系列CPLD配置方法探討

摘 要 :介紹ACEX 1K系列器件的配置方法,對幾種方法進行了分析對比,并著重論述了應用配置器件配置 ACEX 1K系列器件的優點。

關鍵詞 :CPL

2009-06-20 10:51:54 478

478

478

478

FPGA器件的在線配置方法

摘要: 介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數據的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統的設計方法及

2009-06-20 10:57:26 1062

1062

1062

1062

FPGA 重復配置和測試的實現

FPGA 重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括

2009-09-03 11:17:08 528

528

528

528

基于對EPCS在線編程的FPGA可重構方法

基于對EPCS在線編程的FPGA可重構方法

0 引言 可重構體系結構已經成為FPGA系統開發的研究熱點,并已有許多令人矚目的研究成果及產品應用。FPGA可重構

2009-12-08 17:22:17 1310

1310

1310

1310FPGA中SPI復用配置的編程方法

FPGA中SPI復用配置的編程方法

SPI(Serial Peripheral InteRFace,串行外圍設備接口)是一種高速、全雙工、同步的通信總線,在芯片的引腳上只占用4根線,不僅節約了芯片的引

2010-01-06 14:48:18 3062

3062

3062

3062

FPGA重復配置和測試的實現

FPGA重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 544

544

544

544

基于JTAG接口實現ARM的FPGA在線配置設計

基于JTAG接口實現ARM的FPGA在線配置設計

引 言???? 為了解決不同標準間無線接口技術的互通和兼容,人們提出了軟件無線電(Software Defined Radio,SDR)技術

2010-02-09 10:56:10 3142

3142

3142

3142

ARM設計的FPGA可重構配置方法的實現及應用

摘要:文中詳述了FPGA被動串行配置方式的時序,給出配置流程圖及實現的程序代碼,并通過實例驗證了該方法的優越

2010-07-21 14:48:48 1326

1326

1326

1326

使用CPLD和Flash實現FPGA的配置

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點

2018-10-25 05:51:00 8194

8194

8194

8194

一種基于SRAM的FPGA的加密方法

FPGA在現代電子系統設計中,由于其卓越性能、靈活方便而被廣泛使用,但基于SRAM的FPGA需要從外部進行配置,配置數據很容易被截獲,故存遮安全隱患。總結了當前FPGA的加密方法;提出了一種基于外部單片機的FPGA加密方法,該方法中使用外部單片機配合FPGA產生

2011-03-16 14:22:24 48

48

48

48Leon3的接口配置設計

本文設計了采用嵌入到FPGA的Leon3開源CPU軟核來控制實現Virtex系列FPGA的SelectMap接口配置的方法,可將其應用于對FPGA芯片的在線配置。

2011-06-21 12:03:18 1474

1474

1474

1474

Leon3軟核的FPGA SelectMap接口配置設計

本文結合具體應用需求,介紹了利用嵌入式CPU Leon3軟核處理器對Virtex系列FPGA的配置進行控制的方法。此系統能夠實現FPGA配置數據的重構,并且減少了外圍CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3151

3151

3151

3151

微處理器系統中連接簡單的被動串行配置方法和被動并行異步配置方法

摘要: ALTERA公司SRAM工藝可編程器件應用廣泛,專用配置器件比較昂貴。在具有微處理器的系統中,使用微處理器系統的存儲器來存儲配置數據,并通過微處理器配置FPGA,這種方法幾乎不增加

2017-11-06 11:10:48 1

1

1

1V5 FPGA配置回讀

通過SELECTMAP32接口配置和回讀XILINX公司生產的V5系列SRAM型FPGA,被配置的FPGA以下簡稱DUT,產生配置時序的FPGA簡稱配置FPGA。首先硬件上應將M[2:0]接成110

2017-11-17 10:16:01 8730

8730

8730

8730基于測試系統的FPGA測試方法研究與實現

)等部分組成。對FPGA進行測試要對FPGA內部可能包含的資源進行結構分析,經過一個測試配置(TC)和向量實施(TS)的過程,把FPGA配置為具有特定功能的電路,再從應用級別上對電路進行測試,完成電路的功能及參數測試。 2 FPGA的配置方法 對FPGA進行配置有多種方法可以選擇,包括邊界掃描配置方法等。

2017-11-18 10:44:37 2001

2001

2001

2001

反熔絲FPGA配置和編程方法

反熔絲FPGA制造困難且多用在特殊用途領域,因此有關其位流文件的研究很少.本文首先介紹了反熔絲FPGA 及FPGA CAD軟件流程, 接著描述了反熔絲FPGA具體結構并通過一個具體例子說明了如何配置

2017-11-18 11:19:01 10165

10165

10165

10165

FPGA配置與測試的詳細方法分析與特點

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過

2017-11-24 20:55:53 5922

5922

5922

5922

關于fpga編程flash芯片和配置數據技巧

在FPGA中實現在應用編程(In Application Programming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式

2017-12-13 13:58:10 24009

24009

24009

24009

AS配置方式由FPGA器件引導配置操作過程

JTAG模式在線下載FPGA的原理如圖7.15所示,PC端的Quartus II軟件通過下載線纜將bit流(sof文件)下載到FPGA內部,下載完成后FPGA中立刻執行下載代碼,速度很快,非常適合調試。

2018-03-13 09:46:53 11628

11628

11628

11628

FPGA的配置/加載方式

FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數據。

2018-10-05 10:12:00 17251

17251

17251

17251基于ICR技術的FPGA配置電路硬件設計及其工作原理

,FLEX10K可以使用4種配置模式,即:主動串行(AS)、被動串行(PS)、被動并行同步(PPS)、被動并行異步(PPA)。由于PPA配置模式為并行配置,其配置速度快,且配置時鐘由FPGA內部產生,更有利于在線實現,本文就是采用PPA方式來實現電路系統的在線重構。PPA方式配置時應注意以下幾點:

2019-08-21 08:01:00 4908

4908

4908

4908

FPGA配置相關筆記

Altera FPGA支持AS,PS,JTAG等幾種較常見的配置方法。 當為AS配置模式時,FPGA為主設備,加載外部FLASH中的數據至內部RAM中運行。當為PS配置模式時,FPGA為從設備,外部

2018-11-18 18:05:01 481

481

481

481FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明

本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17

17

17以Flash控制器為核心的FPGA在線更新功能實現設計流程介紹

則費時費力且還需拆結構。若在FPGA內部通過邏輯代碼搭建一Flash控制器實現對Flash器件的讀寫操作,即可并行實現系統內每片FPGA對配置文件的在線更新,大大縮短程序固化時間。本文依托于Xilinx

2020-01-27 16:17:00 2747

2747

2747

2747

Spartan-6 FPGA的配置教程說明

Spartan-6 FPGA 利用CCL 支持布線線路與邏輯單元之間的可配置互聯功能。Spartan-6 FPGA 是易失性器件- 電源移除時,不能保留原有配置。為了配置Spartan-6

2020-01-10 15:28:51 25

25

25

25FPGA的配置引腳說明

FPGA是基于SRAM編程的,編程信息在系統掉電時會丟失,每次上電時,都需要從器件外部的FLASH或EEPROM中存儲的編程數據重現寫入內部的SRAM中。FPGA在線加載需要有CPU的幫助,并且在加載前CPU已經啟動并工作。FPGA的加載模式主要有以下幾種:

2020-04-07 08:00:00 16

16

16

16FPGA的三種配置方式詳解

FPGA器件有三類配置下載方式:主動配置方式(AS)和被動配置方式(PS)和最常用的(JTAG)配置方式。AS由FPGA器件引導配置操作過程,它控制著外部存儲器和初始化過程,EPCS系列

2020-07-09 10:53:09 7500

7500

7500

7500基于FPGA器件EP20K200E芯片的配置方式在嵌入式系統中的應用研究

介紹一種在嵌放式系統中使用微處理器被動串行配置方式實現對FPGA配置的方案,將系統程序及配置文件存在系統Flash中,利用微處理器的I/O口產生配置時序,省去配置器件;討論FPGA的各種配置方式

2020-09-29 17:05:59 878

878

878

878

FPGA有哪些主要配置方式?

方式 1、主動配置方式(AS) 2、被動配置方式(PS) 3、JTAG方式 1、AS模式(active serial configuration mode):FPGA器件每次上電時作為控制器,由

2021-03-12 16:26:58 11307

11307

11307

11307

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法(哪些專業適合嵌入式開發)-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 21

21

21

21FPGA芯片配置分類及配置方式

廣義的來說,FPGA的配置包括直接使用下載電纜對FPGA器件進行編程、對外部EEPROM和FLASH進行編程、使用MPU對FPGA器件進行編程、外部EEPROM和FLASH對器件進行編程

2021-09-06 09:41:56 6052

6052

6052

6052FPGA CPLD可編程邏輯器件的在系統配置方法

FPGA CPLD可編程邏輯器件的在系統配置方法(深圳市村田電源技術有限公司)-FPGA CPLD可編程邏輯器件的在系統配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13

13

13?在配置FPGA器件時的常見問題及其解決方法

FPGA器件配置方式分三大類:主動配置、被動配置和JTAG配置。 主動配置:由FPGA器件引導配置操作過程。 被動配置:由計算機或控制器控制配置過程。上電后,控制器件或主控器把存儲在外部存儲器

2022-11-17 12:15:10 1141

1141

1141

1141FPGA配置模式和配置設計

Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置技術,其主要優點是系統設計更加簡單、不需要外部存儲器和配置控制器、功耗低、成本低和FPGA配置時間更快。最大的缺點在于配置是固定的。

2022-12-01 11:08:45 862

862

862

862FPGA在線調試的方法簡單總結

Xilinx被AMD收購的事情把我震出來了,看了看上上一篇文章講了下仿真的文件操作,這篇隔了很久遠,不知道該從何講起,就說說FPGA的在線調試的一些簡單的操作方法總結。

2023-06-19 15:52:21 1225

1225

1225

1225

使用高速NOR閃存配置FPGA

點擊上方 藍字 關注我們 NOR閃存已作為FPGA(現場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數據吞吐量特性使得FPGA在工業、通信和汽車ADAS(高級駕駛輔助系統

2023-08-15 13:55:02 331

331

331

331

電子發燒友App

電子發燒友App

評論