M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVME 80MM SSD PCIE X4 ADAPT

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

M.2 NVME 110MM SSD PCIE X4

2024-03-14 22:02:08

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

8-CH RELAY & 8-CH IDI PCIE CARD

2024-03-14 20:33:38

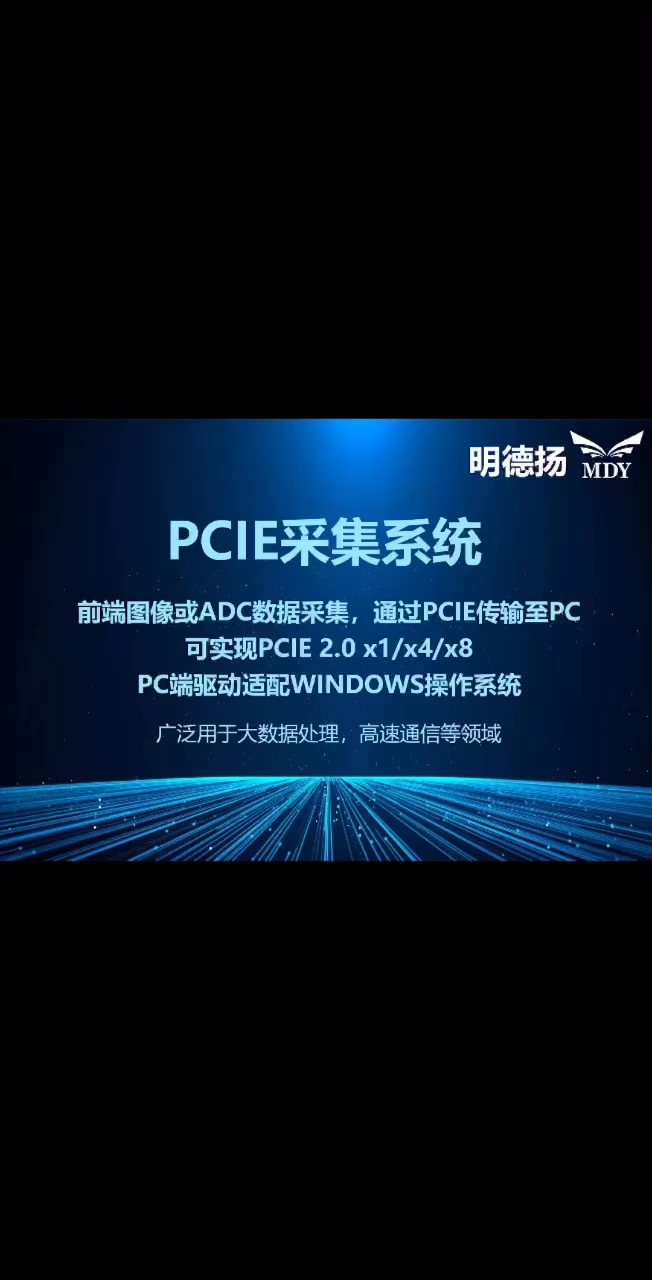

實(shí)時(shí)傳遞到上位機(jī)采集緩沖區(qū)。在超帶寬視頻采集情況下,支持采集丟幀操作,后續(xù)視頻可以正常采集。視頻采集與顯示子系統(tǒng)使用高效的PCIe H2C DMA引擎讀取上位機(jī)顯示緩沖區(qū)的視頻幀,存儲(chǔ)到視頻顯示隊(duì)列中

2024-03-13 13:59:45

Integrated Block,Multi-Channel PCIe RDMA Subsystem實(shí)現(xiàn)了使用DMA Ring緩沖的獨(dú)立多通道、高性能/超低延時(shí)/超低抖動(dòng)Continous Ring DMA

2024-03-07 13:54:29

如圖所示,PCIe IP作為endpoint與RC對(duì)接,用戶實(shí)現(xiàn)了應(yīng)用邏輯,與PCIe IP進(jìn)行交互,交互信號(hào)中data格式為TLP報(bào)文格式,且交互信號(hào)包含相應(yīng)的控制信號(hào),例如PCIe配置空間和IP相干的配置信號(hào)。

2024-02-26 18:19:28 857

857 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem實(shí)現(xiàn)了使用DMA地址隊(duì)列的獨(dú)立多通道、高性能Continous

2024-02-22 11:11:55 151

151

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,實(shí)現(xiàn)PCIe PHY Layer,Data Link Layer以及

2024-02-21 15:15:03 144

144

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503 /步進(jìn)伺服驅(qū)動(dòng)器;(2)聯(lián)動(dòng)軸數(shù)最高可達(dá)16軸,運(yùn)動(dòng)周期最小為100μs;(3)標(biāo)配8進(jìn)8出,其中4路高速鎖存輸入和8路高速PWM、PSO輸出,更多IO請(qǐng)選配ACC37接線板擴(kuò)展板;(4)支持PWM

2024-01-24 09:48:21

隨著PCIE版本的不斷升級(jí),其應(yīng)用范圍也越來越廣泛。除了傳統(tǒng)的顯卡、網(wǎng)卡、聲卡等設(shè)備外,SSD、USB控制器、Thunderbolt接口等設(shè)備也開始支持PCIE接口。

2024-01-21 10:25:10 577

577 高性能20路PCIe時(shí)鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于擴(kuò)充計(jì)算機(jī)系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。目前服務(wù)器

2023-12-20 08:19:38 240

240

)、AD9974的a、b兩通道的寄存器空間是否相互獨(dú)立?

2)、在雙通道的配置過程中,是否應(yīng)當(dāng)有先后順序?

3)、造成無法雙通道同時(shí)使用的原因是什么?

2023-12-18 06:07:03

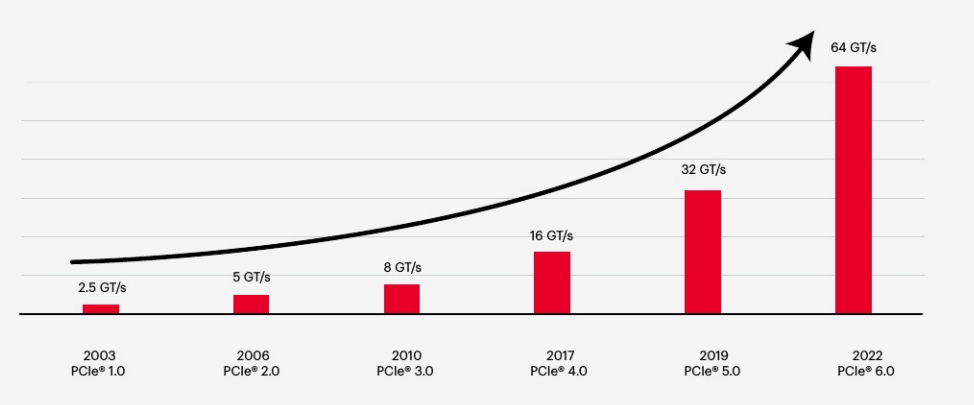

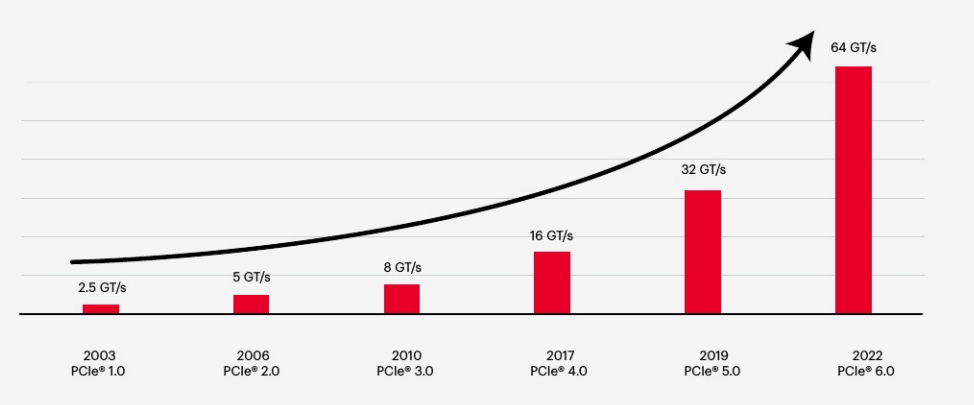

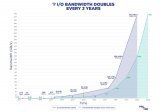

自2003年推出以來,PCIe發(fā)展至今已經(jīng)從最初的1.0升級(jí)到了6.0,本文則為大家簡(jiǎn)單介紹一下PCIe標(biāo)準(zhǔn)的演進(jìn)歷史以及各代PCIe標(biāo)準(zhǔn)之間的主要差異。

2023-12-14 16:38:08 1525

1525

=94%]

[tr][td]

三、應(yīng)用軟件

2路AD采集PCIe傳輸(453 + 536)

軟件實(shí)現(xiàn)FPGA邏輯 AD采集,PCIe XDMA傳輸,寄存器配置

采集顯示上位機(jī)一體,支持2通道AD數(shù)據(jù)

2023-12-11 11:36:40

,PCIe標(biāo)準(zhǔn)幾經(jīng)迭代。PCIe最初作為一種串行接口引入,用于替代眾多主板架構(gòu)使用的并行總線, 但PCIe擁有一項(xiàng)獨(dú)特特性:通道數(shù)量可從1個(gè)擴(kuò)展至32個(gè)。 借助這一并行總線特性,PCIe兼容設(shè)備之間可以根據(jù)數(shù)據(jù)傳輸要求,建立寬度為1個(gè)、2個(gè)、4個(gè)、8個(gè)、16個(gè)甚至高達(dá)32個(gè)通道的鏈路

2023-11-30 12:15:01 310

310

隨著英特爾Alder Lake CPU的發(fā)布,以及AMD 7000 Ryzen CPU的即將發(fā)布,PCIe 5.0 硬件終于成為現(xiàn)實(shí)。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1298

1298

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起來還是挺方便的,生成IP的同時(shí)生成了對(duì)應(yīng)的PCIE

2023-11-17 14:35:30

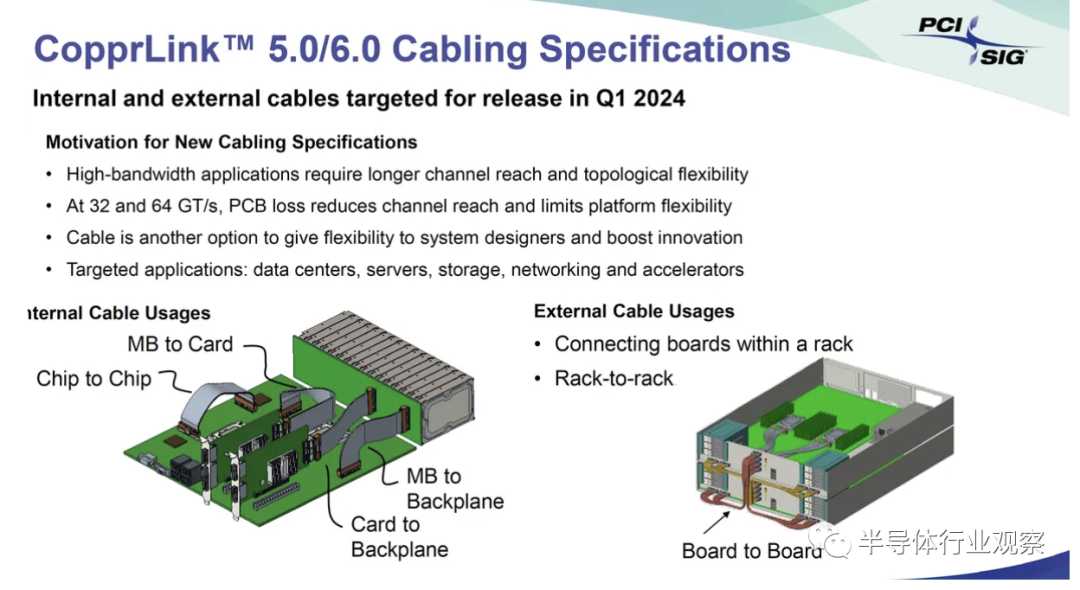

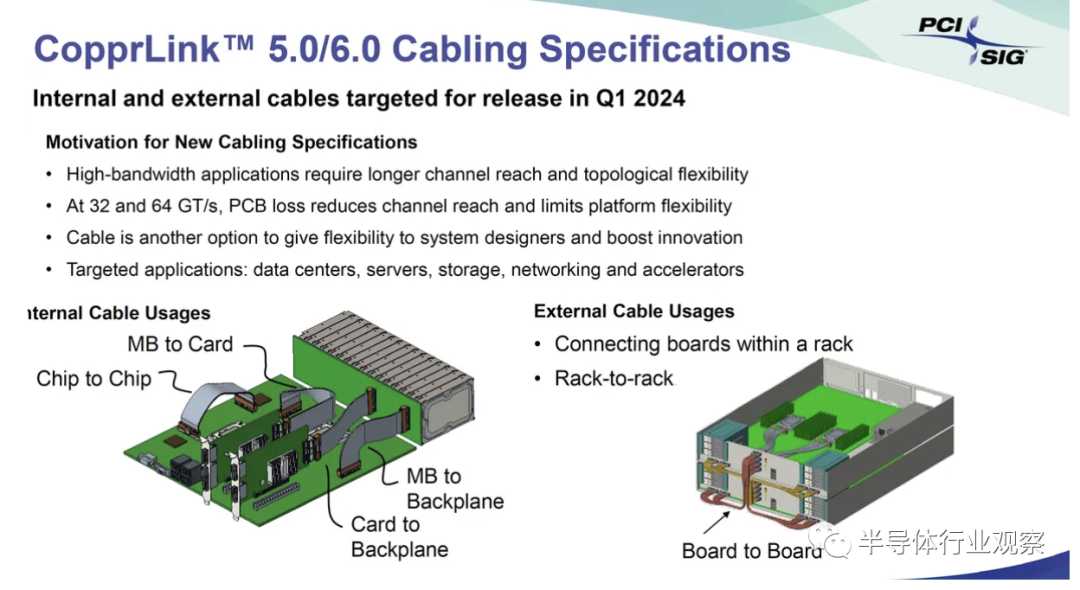

PCI SIG 本周表示,它正在開發(fā) PCIe 5.0 和PCIe 6.0接口的布線規(guī)范,數(shù)據(jù)傳輸速率為 32 GT/s 和 64 GT/s。

2023-11-16 17:43:19 763

763

多種設(shè)備的連接。

2、傳輸速率簡(jiǎn)介

PCIe 分類、速度,按lane的個(gè)數(shù)分有 x1 x2 x4 x8 x16 (最大可支持32個(gè)通道),按代來分 有 gen1 gen2 gen3 gen4

PCIe

2023-11-02 09:31:28

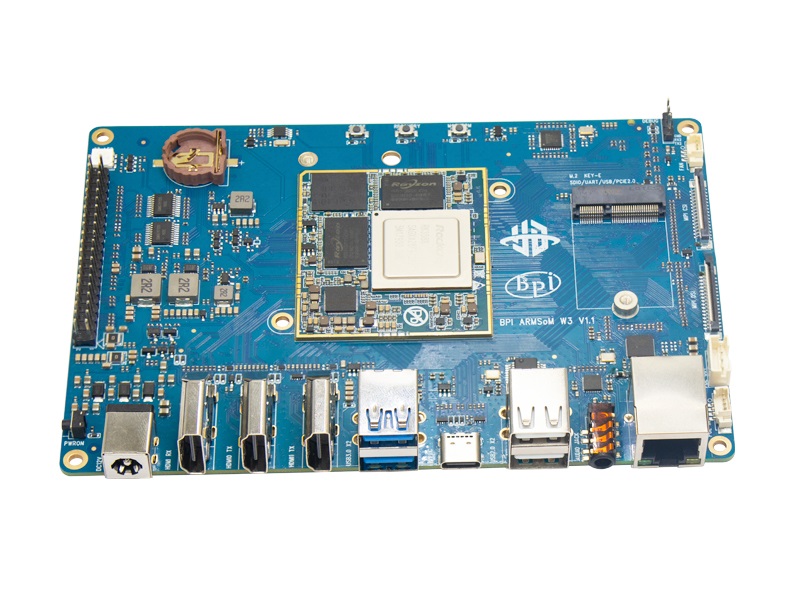

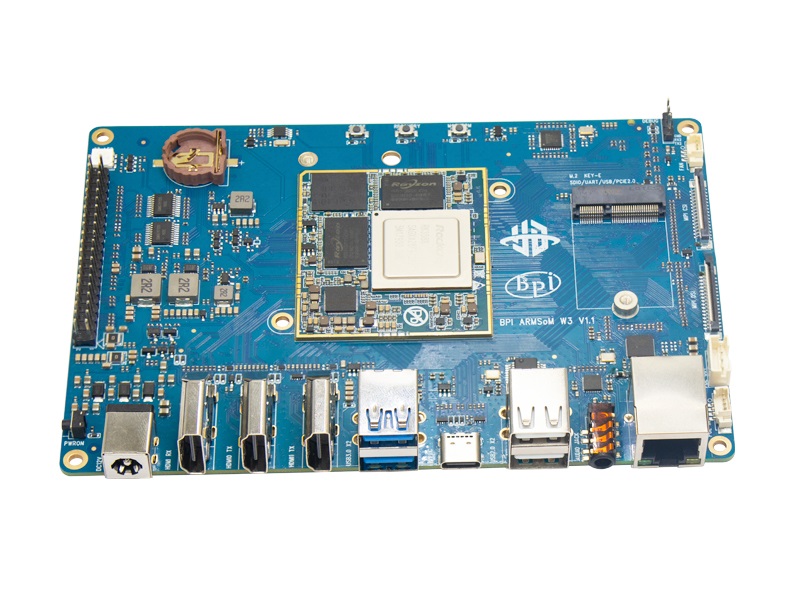

Banana Pi BPI-W3 RK3588平臺(tái)驅(qū)動(dòng)調(diào)試篇 [ PCIE篇 ] - PCIE的開發(fā)指南(二)

2023-11-02 09:24:05 275

275

本文我們將向大家介紹PCIe引腳定義以及PCIe協(xié)議層。

2023-09-26 11:39:14 5629

5629

Atlas200I A2+PCIE X4接口測(cè)試FPGA 實(shí)物圖片

全愛科技QA200A2 Altas200I A2開發(fā)套件做了驗(yàn)證。

圖 1-2 QA200A2 Atlas200I A2 開發(fā)套件實(shí)物圖

2023-09-05 14:39:57

? 我們?cè)谶M(jìn)行PCIe RTL仿真時(shí),由于PCIe ltssm協(xié)商過程比較復(fù)雜,導(dǎo)致PCIe ltssm進(jìn)入L0狀態(tài)所花費(fèi)的時(shí)間比較長(zhǎng)(大概在20~60分鐘,因代碼復(fù)雜度、服務(wù)器性能、PCIe速率

2023-08-17 09:42:22 721

721

本文檔旨在提供關(guān)于將PCIe接口集成到基于AMBA的片上系統(tǒng)(SoC)的指導(dǎo)。

假設(shè)PCIe接口通過基于AXI或ACE協(xié)議的互連連接到SoC的其余部分。

讀者應(yīng)熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX4950ACTX+T相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有MAX4950ACTX+T的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,MAX4950ACTX+T真值表,MAX4950ACTX+T管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-08-15 18:50:47

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX4950CTO+T相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有MAX4950CTO+T的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,MAX4950CTO+T真值表,MAX4950CTO+T管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-08-15 18:50:23

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX4950ACTX+相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有MAX4950ACTX+的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,MAX4950ACTX+真值表,MAX4950ACTX+管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-08-15 18:45:11

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX4950CTO+相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有MAX4950CTO+的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,MAX4950CTO+真值表,MAX4950CTO+管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-08-15 18:42:42

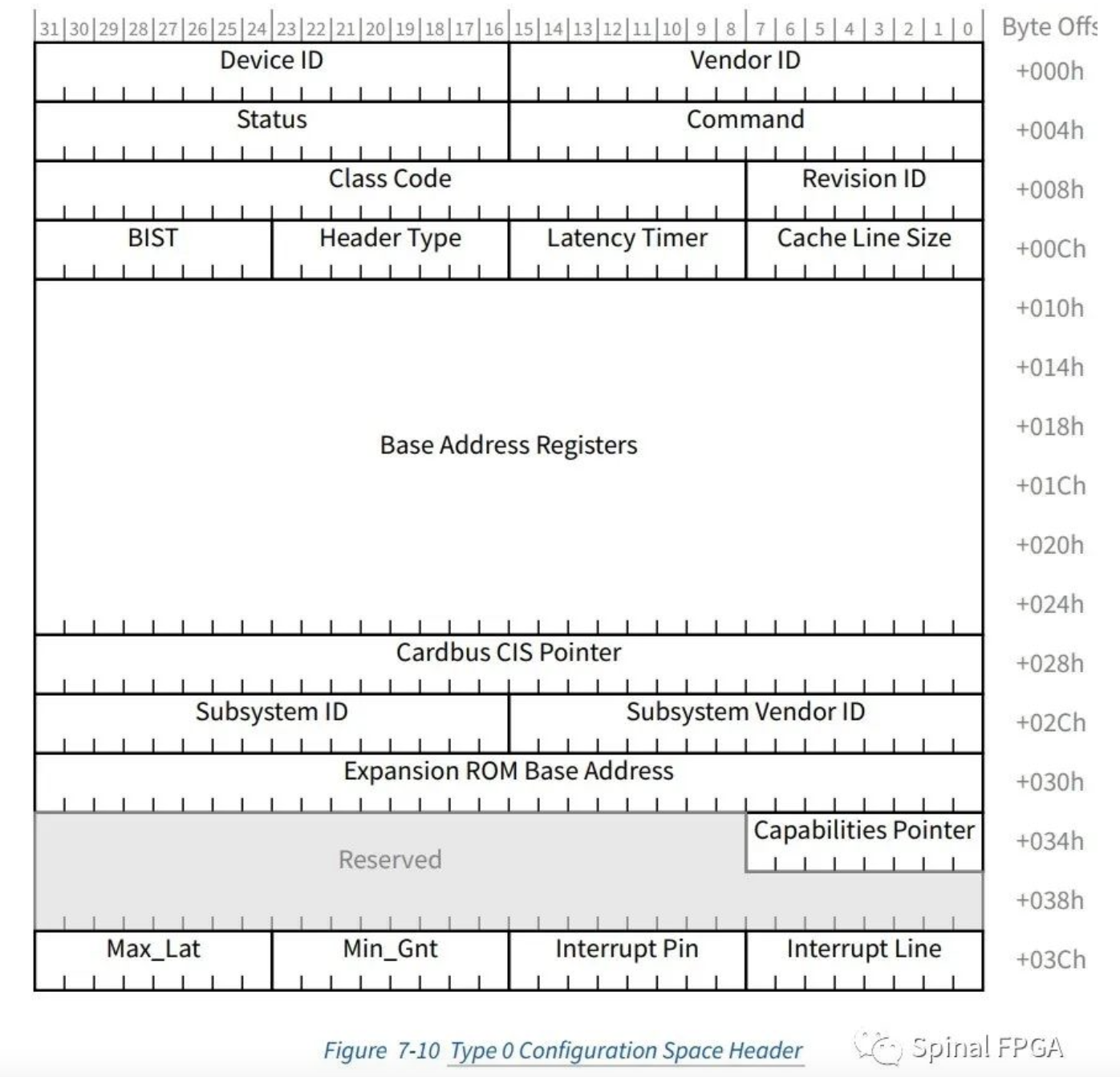

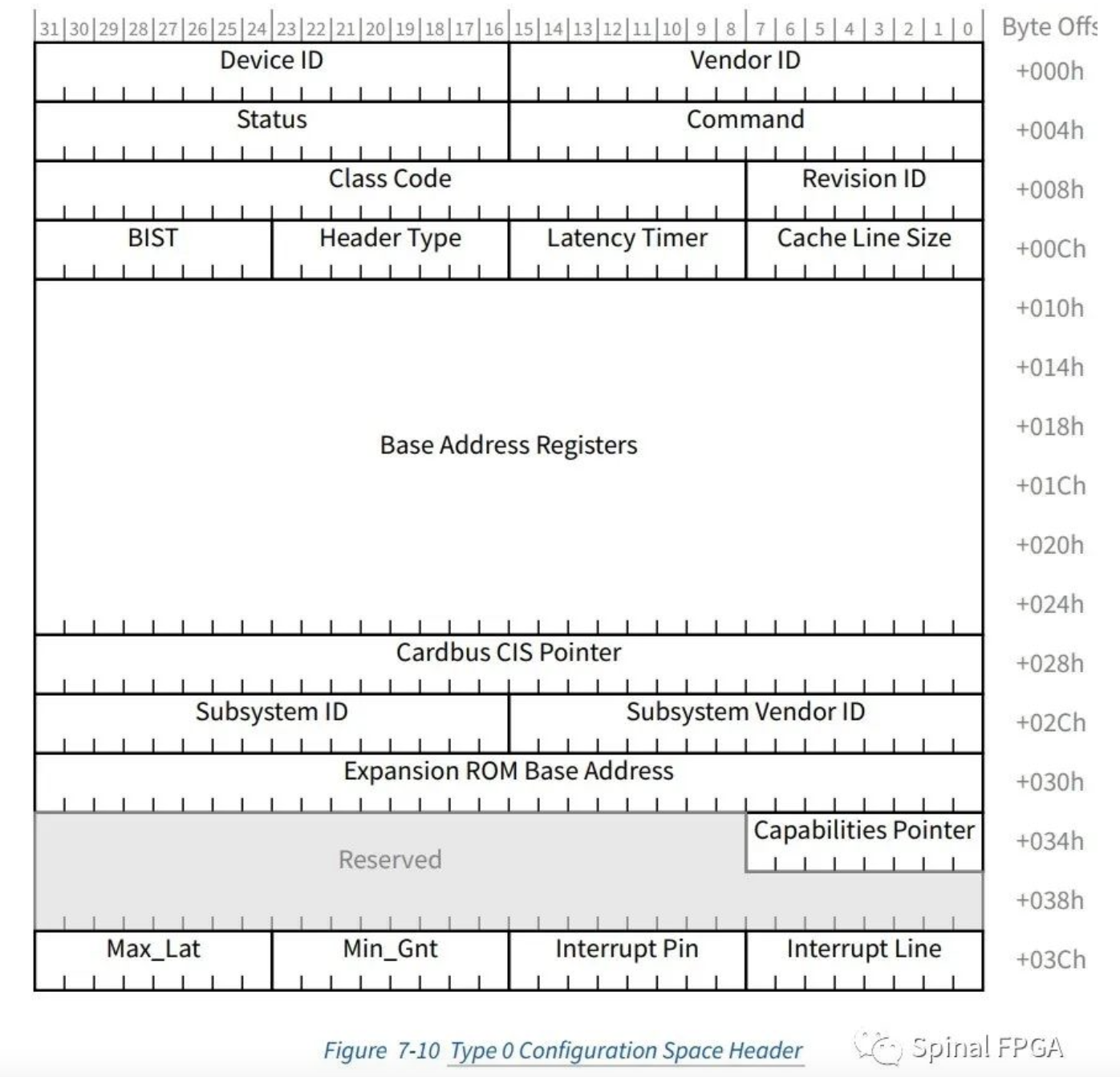

訪問 PCI/PCIe 設(shè)備的流程 PCI/PCIe 設(shè)備的配置信息 PCI/PCIe 設(shè)備上有配置空間(配置寄存器),用來表明自己"需要多大的地址空間"。 注意,這是 PCI/PCIe 地址空間

2023-07-30 09:44:54 941

941 自2003年推出以來,PCIe發(fā)展至今已經(jīng)從最初的1.0升級(jí)到了6.0,在上一篇文章中為大家介紹了PCIe基礎(chǔ)知識(shí):《什么是PCIe?》 ,本文則為大家簡(jiǎn)單介紹一下 PCIe 標(biāo)準(zhǔn)的演進(jìn)歷史以及

2023-07-26 08:05:01 867

867

要充分發(fā)揮PCIe 4.0的優(yōu)勢(shì),需要具備兼容PCIe 4.0的主板和設(shè)備。如果你的設(shè)備只支持PCIe 3.0,那么你將無法享受到PCIe 4.0的速度和帶寬優(yōu)勢(shì)。

2023-07-18 15:10:30 18123

18123 PCIe是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來,已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡(jiǎn)單介紹一下PCIe的發(fā)展歷史以及它的工作原理。 一、PCIe的由來

2023-07-04 18:15:03 9759

9759 如果不是做主板類的工程師或者沒有自己組裝過電腦/服務(wù)器的,估計(jì)很多人并不了解PCIe是什么。

2023-07-04 09:30:03 5044

5044

最近在研究cocotbext-pcie的實(shí)現(xiàn),對(duì)于學(xué)習(xí)PCIe還是挺有幫助的,陸陸續(xù)續(xù)做個(gè)總結(jié),有時(shí)間也會(huì)在SpinalHDL下實(shí)現(xiàn)類似的方針功能。

2023-07-03 17:47:34 2282

2282

MAX13256具有可調(diào)過流門限,用于短路保護(hù)。不幸的是,這個(gè)閾值使得使用標(biāo)準(zhǔn)方法為設(shè)備設(shè)計(jì)緩沖器變得困難。本應(yīng)用筆記介紹了如何為MAX13256設(shè)計(jì)電壓緩沖器,同時(shí)考慮限流特性。

2023-06-25 14:22:18 582

582

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 506

506

??編 者 按? ? ????讀cocotbext-pcie源碼,有部分牽涉到數(shù)據(jù)鏈路層。雖然自工作以來接觸到PCIe還是蠻多的,但一般往往專注在TLP層,對(duì)于數(shù)據(jù)鏈路層還是接觸的比較少的。PCIe

2023-06-25 10:31:17 1457

1457

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-21 11:32:14 494

494

PCIe M.2 接口規(guī)范

2023-06-19 10:02:30 18

18 refclk1(硬件上已固定),可參考下圖:

4. 其他設(shè)置可保持默認(rèn),點(diǎn)擊 Generate 生成 PCIE IP;:

5.關(guān)閉本工程,按此路徑打開 Example 工程:

2

2023-06-13 15:50:05

我是一名PCIe新手,想了解以下問題:

1、如何測(cè)試PCIe?

2、如何讀寫PCIe(兩塊開發(fā)板通過PCIe線互連,分別配置為RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

/class/pci_epc 中使用 pcie 端點(diǎn)控制器,并在根復(fù)合體端 (x86) 上使用 lspci 和 pcitest 測(cè)試接口。

問題是,PCIe端點(diǎn)控制器設(shè)備不存在(/sys/class

2023-06-09 08:23:25

高性能的時(shí)鐘器件是高帶寬、高速率、高算力、大模型的基礎(chǔ)。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應(yīng)用的超低抖動(dòng)全新20路LP-HCSL差分時(shí)鐘緩沖器CLB2000,其業(yè)界領(lǐng)先的附加抖動(dòng)性能遠(yuǎn)超PCIe Gen 5和PCIe Gen 6的標(biāo)準(zhǔn)。

2023-06-08 15:30:21 526

526

高性能的時(shí)鐘器件是高帶寬、高速率、高算力、大模型的基礎(chǔ)。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應(yīng)用的超低抖動(dòng)全新20路LP-HCSL差分時(shí)鐘緩沖器CLB2000,其業(yè)界領(lǐng)先的附加抖動(dòng)性能遠(yuǎn)超PCIe Gen 5和PCIe Gen 6的標(biāo)準(zhǔn)。

2023-06-08 15:29:55 805

805

Layerscape MPU 中是否有支持 PCIe GEN3 16 通道的 EVB?

2023-05-30 08:01:56

PCI Express? 6.0 (PCIe? 6.0) 規(guī)范由 PCI-SIG? 于 2022 年 1 月發(fā)布。最新一代的 PCIe 標(biāo)準(zhǔn)帶來了許多激動(dòng)人心的新功能,旨在提高計(jì)算密集型工作負(fù)載的性能,包括數(shù)據(jù)中心、 AI/ML 和 HPC 應(yīng)用程序

2023-05-22 17:27:51 4386

4386

ZYNQ7045的PCIE電路設(shè)計(jì),板卡使用插針式連接器,引出了PCIE信號(hào),未使用金手指。為了插入機(jī)箱設(shè)計(jì)了擴(kuò)展版,插座與插針對(duì)應(yīng),帶有PCIE金手指。目前遇到的問題是,當(dāng)板卡連接擴(kuò)展板使用金手指

2023-05-16 11:07:40

有沒有辦法確認(rèn) i.MX6SX PCIe RX 終端的設(shè)置。我在 i.MX6SX 上看到 PCIe 實(shí)現(xiàn)的 PCIe RX SI 結(jié)果可能表明 RX 終端設(shè)置為 OFF,我正在尋找一種方法來確認(rèn)。PCIe PHY 寄存器沒有內(nèi)存映射,我不確定控制器是否正在更改設(shè)置。

2023-05-12 06:40:33

差分探頭是一種常用的測(cè)試儀器,在PCIE測(cè)試中也有廣泛的應(yīng)用。本文將介紹差分探頭在PCIE測(cè)試上的應(yīng)用及其優(yōu)勢(shì)。

2023-05-11 10:54:14 450

450 你好

作為我們?cè)?ls1028 上努力的一部分

我們通過 pcie 將自定義 fpga 連接到 M.2 連接器(通道 C/2 - j16)

相關(guān)uboot日志:

U-Boot

2023-05-09 12:00:30

我們可以將多個(gè) PCIe 設(shè)備 (IC) 連接到一般的單個(gè) PCIe 控制器(在我們的案例中更具體地說是 NXP LS20xxA 處理器)嗎?

例如,將四個(gè)不同的 PCIe x1 設(shè)備 (IC

2023-05-05 07:35:41

我們有將 SATA HDD 連接到 IMX8M Plus 處理器的要求,但我們只有單通道 PCIe 3.0 接口。

您能否建議從PCIe到sat接口的轉(zhuǎn)換器以支持外部硬盤驅(qū)動(dòng)器(最大 2TB)

2023-05-04 07:19:49

我們有兩張 LS1028a 卡通過背板連接,一張卡運(yùn)行 RCW,選擇 PCIe_RC,另一張卡選擇 PCIe_EP。這些卡與 Flexbuild v2012 U-Boot & Linux 一起移植。

如何證明這些處理器之間通過 PCIe 接口進(jìn)行數(shù)據(jù)通信?

2023-05-04 06:04:29

液壓緩沖器強(qiáng)度是否能夠調(diào)節(jié),取決于液壓緩沖器的種類,目前市面上較為常用的液壓緩沖器包括可調(diào)液壓緩沖器、不可調(diào)液壓緩沖器,這兩種緩沖器調(diào)節(jié)強(qiáng)度的實(shí)際效果是不一樣的。

2023-04-24 16:12:01 2147

2147 類型控制 PCIe 控制器設(shè)備類型、PHY 類型、SRIS 模式和手動(dòng)通道翻轉(zhuǎn)啟用。0000b - 端點(diǎn)0100b - 根聯(lián)合體的根端口0110b - 上游交換機(jī)端口所有其他值均保留。在我寫入寄存器

2023-04-18 07:45:06

帶 2GB DDR3 的定制 LS1043A 板。我們?cè)?PCIe 通道和 2 GbE RGMII 端口上有一個(gè) M.2 WiFi 卡。他們中的任何一個(gè)都會(huì)使用 iPerf 自行完成一個(gè) Gb

2023-04-18 07:30:13

+ ) 已設(shè)置。但是設(shè)置這個(gè)寄存器的代碼在兩個(gè)不同版本的驅(qū)動(dòng)程序中也有很大不同。有沒有人設(shè)法讓 PCIe 與主線內(nèi)核驅(qū)動(dòng)程序一起工作?我覺得它應(yīng)該經(jīng)過測(cè)試,并且應(yīng)該有效。移植驅(qū)動(dòng)程序似乎很麻煩,因?yàn)檎麄€(gè) phy 接口已經(jīng)改變了很多。

2023-04-14 08:12:05

PCIe接口從2001年發(fā)展至今,在協(xié)議的完整性上已經(jīng)建立足夠高的"護(hù)城河",重新定義一個(gè)接口協(xié)議在性能上超越PCIe,短期內(nèi)一方面沒有企業(yè)會(huì)有這個(gè)動(dòng)力,另一方面技術(shù)的維度,也沒有可預(yù)期的雛形創(chuàng)新。

2023-04-13 11:10:00 2899

2899 IC CLOCK GENERATOR PCIE 42TQFN

2023-04-06 15:33:36

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:30

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:25

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:33:53

我對(duì)第 3 代存儲(chǔ)進(jìn)行了測(cè)試。但是 LS1046A RDB 指示此存儲(chǔ)是 Gen2。那么,我的問題是:LS1046ARDB 是否支持 PCIE 3.0?

2023-04-06 06:30:54

M31 PCIe 5.0 PHY IP,用于存儲(chǔ)和高帶寬連接 M31 PCIe 5.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

用于存儲(chǔ)和高帶寬連接的M31 PCIe 4.0 PHY IP–具有16GT/s的最高速度PCIe 4.0 PHY IP M31 PCIe 4.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道

2023-04-03 19:54:58

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本應(yīng)

2023-04-03 19:50:56

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收發(fā)器IP提供了一系列完整的PCIe 2.1基本應(yīng)用程序。它符合PIPE 3.0規(guī)范。該IP集成了高速混合信號(hào)電路,以支持

2023-04-03 19:47:28

是 VDD_PCIE_DIG_1P8_3P3引腳——我們?cè)诙ㄖ瓢逯袑⑵湓O(shè)置為 1v8。但是,MEK 板使用 3v3。定制板i.MX8QXP-MEK VDD_PCIE_DIG_1P8_3P3電壓變化是否也需要更改設(shè)備樹?PHY 鏈路問題是否是由模塊和處理器之間的阻抗不匹配引起的?

2023-04-03 06:31:15

我在訪問 PCIe BAR 空間時(shí)遇到 Async Serror。很奇怪。能幫忙看看是什么原因嗎?謝謝。 ?#dmesg | grep pcie [0.000000] 內(nèi)核命令行:console

2023-04-03 06:06:54

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

QM5i系列虹科Spectrum推出兩款全新PCIe數(shù)字化儀卡。新產(chǎn)品憑借卓越的GHz信號(hào)采集和分析能力,使虹科M5i系列旗艦產(chǎn)品再度升級(jí)。單通道和雙通道的新產(chǎn)品不僅擁有10GS/s的超快采樣率

2023-03-30 10:40:48 488

488

PCIE-52P90H

2023-03-29 22:43:17

1、問題:RK3568平臺(tái)開機(jī)后,插網(wǎng)線,lspci 查找不到PCIe設(shè)備,請(qǐng)問如何進(jìn)一步定位問題點(diǎn)?2、dtsi配置vcc3v3_pcie: gpio-regulator {compatible

2023-03-29 15:01:34

PCIe 3.0,2 通道(4 通道),差分 2:1 Mux/DeMux。3.3V

2023-03-28 12:41:12

與PCI/PCIX橋在PCI/PCIX總線體系結(jié)構(gòu)中的作用類似,PCI Express(PCIE)交換機(jī)的功能是擴(kuò)展連接以允許PCIE串行互連中的主機(jī)控制器訪問更多的終端設(shè)備建筑學(xué)16通道PCIe

2023-03-27 10:54:11 1

1 我想為我們的項(xiàng)目使用 LX2080A 處理器,它只有 2 個(gè) USB 3.0 控制器。我的項(xiàng)目需要五個(gè) USB 端口。我想知道我是否可以在其中一個(gè) USB 控制器中使用 USB 集線器 IC(具有

2023-03-27 08:54:43

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論