深圳市富利威科技有限公司主營TI,ADI,LATTICE,CYPRESS,SEMTECH,ST,,ITE,ON,瑞昱,芯科等眾多國內(nèi)外知名品牌芯片,客戶群體覆蓋安防通訊、消費(fèi)類電子、工業(yè)控制、醫(yī)療

2024-03-18 17:48:34

Xilinx FPGA芯片擁有多個(gè)系列和型號(hào),以滿足不同應(yīng)用領(lǐng)域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點(diǎn)。

2024-03-14 16:24:41 213

213 我目前正在探索將英飛凌 XMC4300 從控制器與

Xilinx Spartan-

6 FPGA 集成到我們項(xiàng)目中的兼容性和通信協(xié)議選項(xiàng)。 具體來說,我想了解 XMC4300 是否適用于促進(jìn)我們?cè)?/div>

2024-03-06 07:47:12

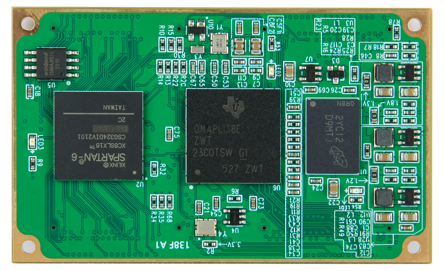

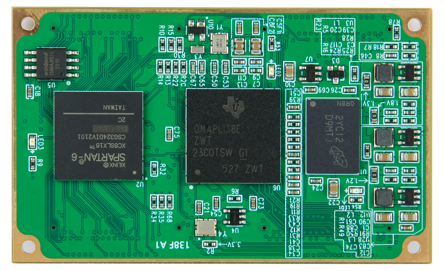

開發(fā)板本身有兩個(gè)種配置,一種是Xilinx Spantan-6 XC6SL16,另外一種是貼國產(chǎn)FPGA-EQ6HL45,是國產(chǎn)中科億海微的自研FPGA。很顯然我拿到的開發(fā)板是后者。

既然如此

2024-02-23 20:51:11

),頻率最高達(dá)456M

FPGA

Xilinx Spantan-6 XC6SL16,可升級(jí)至XC6SL45(可貼國產(chǎn)FPGA)

內(nèi)存

128MB工業(yè)級(jí)DDR2(256MB可選)

存儲(chǔ)

4Gb工業(yè)級(jí)

2024-01-28 08:21:18

FPGA設(shè)計(jì)高級(jí)技巧 Xilinx篇

2024-01-08 22:15:53

目前一個(gè)項(xiàng)目用Xilinx Spantan-6控制AD9253,輸入CLK為10MHz,FPGA程序下載后,ADC有時(shí)輸出的數(shù)據(jù)異常(ADC輸入端接固定電平,輸出的數(shù)據(jù)跳變),需要多次開關(guān)電,才能

2023-12-18 07:41:39

芯片的知識(shí)以及特點(diǎn)。 一、7系列芯片的工藝級(jí)別 xilinx 7系列FPGA芯片采用的是28nm生產(chǎn)工藝,主要分為Spartan、Artix、Kintex和Virtex四個(gè)系列。 ? Xilinx

2023-11-28 10:20:02 390

390

xilinx的FPGA,BANK引腳VREF,VRN,VRP都是什么意思?如何使用,DATASHEET沒看明白,謝謝請(qǐng)幫忙解答謝謝!

補(bǔ)充一下:Virtex II Pro,XC2VP4,謝謝

2023-11-28 07:19:03

Xilinx 7系列芯片應(yīng)用非常廣泛,具有成本低、性能強(qiáng)悍、成熟穩(wěn)定的特點(diǎn),目前Xilinx(AMD)已延長(zhǎng)該系列芯片的生命周期至少到2035年。

2023-11-27 09:26:10 418

418

Xilinx Block Memory Generator(BMG)是一個(gè)先進(jìn)的內(nèi)存構(gòu)造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優(yōu)化的內(nèi)存。

2023-11-14 17:49:43 736

736

項(xiàng)目背景,在DSP上掛Fatfs文件系統(tǒng),而SD卡是掛在FPGA上的,DSP需要通過FPGA與SD卡交互,大概就是會(huì)把數(shù)據(jù)存到FPGA的DDR上,然后FPGA再對(duì)SD卡進(jìn)行讀寫操作。

問題:SD卡在

2023-11-14 09:30:56

。

在全球市場(chǎng)中,Xilinx、Altera兩大公司對(duì)FPGA的技術(shù)與市場(chǎng)仍然占據(jù)絕對(duì)壟斷地位。兩家公司占有將近90%市場(chǎng)份額,專利達(dá)6000余項(xiàng)之多,而且這種壟斷仍在加強(qiáng)。同時(shí),美國政府對(duì)我國

2023-11-08 17:19:01

羅徹斯特電子攜手AMD/Xilinx,為Xilinx傳統(tǒng)FPGA和相關(guān)配置PROM產(chǎn)品提供供貨支持。

2023-11-07 09:04:42 250

250 一、查找表(Look-Up-Table)的原理與結(jié)構(gòu)

采用這種結(jié)構(gòu)的PLD芯片我們也可以稱之為FPGA:如altera的ACEX、APEX系列、Xilinx的Spartan、Virtex系列等

2023-11-03 11:18:38

方法1.通過狀態(tài)機(jī)來實(shí)現(xiàn),通過verilog控制FPGA,讓它該快的時(shí)候快,該慢的時(shí)候慢。

2023-11-02 09:48:18 333

333

MCU(Microcontroller Unit)、DSP(Digital Signal Processor)和FPGA(Field-Programmable Gate Array)是嵌入式系統(tǒng)中常見的三種處理器類型,它們之間有以下主要區(qū)別:。

2023-10-26 10:12:46 1660

1660 電子發(fā)燒友網(wǎng)站提供《基于DSP和FPGA的通用控制器設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-25 10:57:56 0

0 電子發(fā)燒友網(wǎng)站提供《基于Virtex-5FPGA的系統(tǒng)監(jiān)測(cè)器設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-19 10:49:30 0

0 電子發(fā)燒友網(wǎng)站提供《基于DSP和FPGA的水聲定位系統(tǒng)主控機(jī)設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-19 10:26:33 0

0 fpga與dsp通訊怎樣同步時(shí)鐘頻率?dsp和fpga通信如何測(cè)試? 在FPGA與DSP通訊時(shí),同步時(shí)鐘頻率非常重要,因?yàn)椴煌脑O(shè)備有不同的時(shí)鐘頻率,如果兩者的時(shí)鐘頻率不同步,會(huì)導(dǎo)致通訊數(shù)據(jù)的錯(cuò)誤

2023-10-18 15:28:13 1059

1059 一、板卡概述

板卡基于6U VPX標(biāo)準(zhǔn)結(jié)構(gòu),北京太速科技板卡包含一個(gè)C6678 DSP芯片,一個(gè)XCVU9P 高性能FPGA,雙路HPC FMC。二、處理板技術(shù)指標(biāo)

?DSP處理器采用TI 8核

2023-10-16 11:12:06

處理器,主頻456MHz,高達(dá)3648MIPS和2746MFLOPS的運(yùn)算能力;FPGA采用中科億海微eHiChip 6家族EQ6HL45系列芯片,或Xilinx

2023-10-12 16:18:40

電子發(fā)燒友網(wǎng)站提供《基于FPGA+DSP模式的智能相機(jī)設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-08 10:37:16 0

0 Xilinx 從 Spartan-6 和 Virtex-6 器件開始采用高級(jí)可擴(kuò)展接口 (AXI) 協(xié)議作為知識(shí)產(chǎn)權(quán) (IP) 內(nèi)核。Xilinx 繼續(xù)將 AXI 協(xié)議用于針對(duì) 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 593

593

安富萊STM32F103ZE-EK開發(fā)板原理圖

2023-09-19 07:45:01

電子發(fā)燒友網(wǎng)站提供《如何將Arm Cortex-M處理器與Xilinx的FPGA和SoC結(jié)合使用.pdf》資料免費(fèi)下載

2023-09-15 15:04:38 1

1 Xilinx是一家專業(yè)的可編程邏輯器件(PLD)廠商,其產(chǎn)品包括FPGA、CPLD、SOC等。Xilinx的FPGA產(chǎn)品線有多個(gè)系列,其中7系列和Ultrascale系列是比較常見的兩種。那么,這兩個(gè)系列有什么區(qū)別呢?

2023-09-15 14:44:54 1765

1765

本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。

2023-09-15 09:14:26 1941

1941

電子發(fā)燒友網(wǎng)站提供《在Virtex-6 FPGA中使用全數(shù)字VCXO替換技術(shù)實(shí)現(xiàn)三倍速率SDI直通.pdf》資料免費(fèi)下載

2023-09-14 14:52:17 3

3 電子發(fā)燒友網(wǎng)站提供《為新時(shí)代高性能航天級(jí)Xilinx FPGA供電.pdf》資料免費(fèi)下載

2023-09-14 11:24:36 0

0 電子發(fā)燒友網(wǎng)站提供《面向Xilinx FPGA和SoC的超快設(shè)計(jì)方法指南.pdf》資料免費(fèi)下載

2023-09-14 10:02:31 1

1 電子發(fā)燒友網(wǎng)站提供《Xilinx FPGA和SoC的超高速設(shè)計(jì)方法指南.pdf》資料免費(fèi)下載

2023-09-14 09:41:06 0

0 FPGA pcie dma測(cè)試

流程:金手指和電腦連接之后,先加載程序,pc重啟;

現(xiàn)象:pc無法開機(jī)。

FPGA pcie x8,pc x16,直接連接上去的

請(qǐng)問這是什么情況呀,為什么電腦開不了機(jī)呢?

2023-09-13 18:21:28

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應(yīng)用,演示了TopJTAG Probe軟件的應(yīng)用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應(yīng)用,兩者幾乎是一樣。

2023-09-13 12:29:37 654

654

電子發(fā)燒友網(wǎng)站提供《Virtex UltraScale+ FPGA數(shù)據(jù)手冊(cè):DC和AC開關(guān)特性.pdf》資料免費(fèi)下載

2023-09-13 09:45:36 0

0 電子發(fā)燒友網(wǎng)站提供《適用于Xilinx Ultrascale+ FPGA的PMBus穩(wěn)壓器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2023-09-13 09:34:17 0

0 上文XILINX FPGA IP之FIFO對(duì)XILINX FIFO Generator IP的特性和內(nèi)部處理流程進(jìn)行了簡(jiǎn)要的說明,本文通過實(shí)際例子對(duì)該IP的使用進(jìn)行進(jìn)一步的說明。本例子例化一個(gè)讀數(shù)據(jù)位寬是寫數(shù)據(jù)位寬兩倍的FIFO,然后使用讀時(shí)鐘頻率:寫時(shí)鐘頻率=2:3,進(jìn)行簡(jiǎn)單的FIFO跨時(shí)鐘域操作。

2023-09-07 18:31:35 758

758

不友好. 二、FPGA中的加減乘除 1.硬件資源 Xilinx 7系列的FPGA中有DSP Slice ,叫做“DSP48E1”這一專用硬件資源,這是一個(gè)功能強(qiáng)大的計(jì)算單元,單就用于基本運(yùn)算的部分有加減單元和乘法器。詳見參考文獻(xiàn)1. 因此可以直接用HDL語言中的加、減、乘符號(hào)實(shí)現(xiàn)變

2023-09-05 11:45:02 267

267 描述 Virtex?-7 FPGA 針對(duì) 28nm 系統(tǒng)性能與集成進(jìn)行了優(yōu)化,可為您的設(shè)計(jì)帶來業(yè)界最佳的功耗性能比架構(gòu)、DSP 性能以及 I/O 帶寬。 該系列可用于 10G 至 100G

2023-09-01 10:41:54

外部存儲(chǔ)器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 2348

2348

通過上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

Keithley6485吉時(shí)利6485皮安表吉時(shí)利5位半數(shù)字的6485皮安計(jì),結(jié)合了吉時(shí)利在靈敏電流測(cè)量?jī)x器方面的專業(yè)知識(shí),具有更高的速度和堅(jiān)固的設(shè)計(jì)。吉時(shí)利6485具有8個(gè)電流測(cè)量范圍

2023-08-18 16:43:43

是一款基于FPGA的數(shù)字信號(hào)處理器,其采用了Xilinx Virtex-6 XC6VLX760型號(hào)的FPGA。 Xilinx Virtex-6序列是Xilinx公司推出的一款高性能FPGA芯片,采用了

2023-08-16 11:15:40 717

717 適用于需要將小型處理器集成到FPGA中的深度嵌入式應(yīng)用。

該處理器實(shí)現(xiàn)ARMv6-M架構(gòu),并與用于ASIC實(shí)現(xiàn)的Cortex-M0和Cortex-M0+處理器密切相關(guān)。

本章介紹了Cortex-M1 DesignStart FPGA-Xilinx版的功能和目錄結(jié)構(gòu)。

2023-08-16 06:10:25

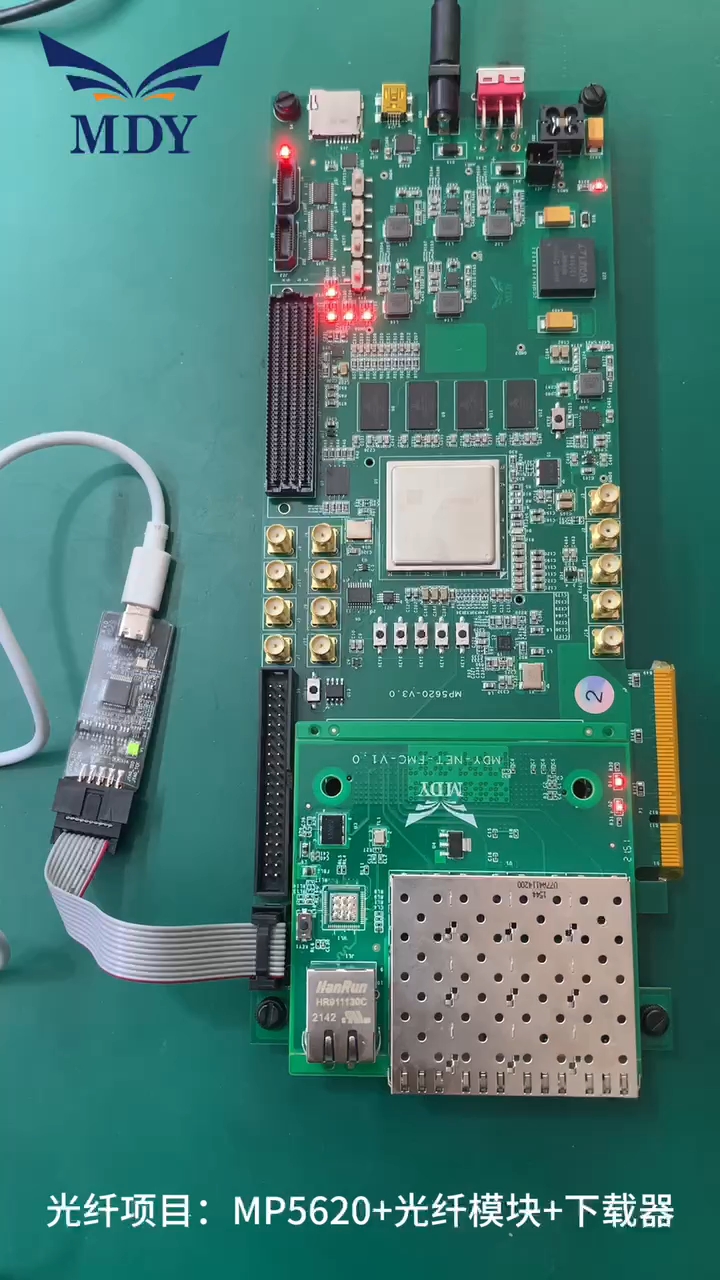

該DSP+FPGA高速信號(hào)采集處理板由我公司自主研發(fā),包含一片TI DSP TMS320C6678和一片Xilinx FPGA K7 XC72K325T-1ffg900。包含1個(gè)千兆網(wǎng)口,1個(gè)FMC

2023-08-15 10:43:15 1126

1126

Xilinx 7系列FPGA全系內(nèi)置了一個(gè)ADC,稱呼為XADC。

2023-08-15 09:19:25 695

695

Cortex-M3 DesignStart?現(xiàn)場(chǎng)可編程門陣列-Xilinx版封裝提供了一種在Xilinx Vivado設(shè)計(jì)環(huán)境中使用Cortex-M3處理器的簡(jiǎn)單方法。

Cortex-M3處理器專為

2023-08-12 07:02:46

星嵌DSP+ARM+FPGA三核核心板(OMAPL138+Xilinx FPGA)

2023-08-01 16:25:21 340

340

概述詳情:Virtex@-7 T和XT FPGAs可在-3、-2、-1和-2L級(jí)速度等級(jí),其中-3級(jí)性能最高。-2L器件在VCCINT=1.0V時(shí)工作,并被屏蔽以獲得較低的最大靜態(tài)功率。速度規(guī)格

2023-07-25 14:46:49

。Xilinx FPGA7系列分為全局時(shí)鐘(Global clock)和局部時(shí)鐘(Regional clock)資源。目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期

2023-07-24 11:07:04 655

655

的硬件結(jié)構(gòu)和開發(fā)特性使得其對(duì)很多算法不友好,之前本人零散地總結(jié)和轉(zhuǎn)載了些基本的數(shù)學(xué)運(yùn)算在FPGA中的實(shí)現(xiàn)方式,今天做一個(gè)系統(tǒng)的總結(jié)歸納。 二、FPGA中的加減乘除 1.硬件資源 Xilinx 7系列的FPGA中有DSP Slice ,叫做“DSP48E1”這一專用硬件資源,這是一個(gè)功

2023-07-19 14:25:02 794

794

OFDM中調(diào)制使用IFFT,解調(diào)使用IFFT,在OFDM實(shí)現(xiàn)系統(tǒng)中,F(xiàn)FT和IFFT時(shí)必備的關(guān)鍵模塊。在使用Xilinx的7系列FPGA(KC705)實(shí)現(xiàn)OFDM系統(tǒng)時(shí),有以下幾種選擇。

2023-07-10 10:50:52 604

604

筆者在校的科研任務(wù),需要用FPGA搭建OFDM通信系統(tǒng),而OFDM的核心即是IFFT和FFT運(yùn)算,因此本文通過Xilinx FFT IP核的使用總結(jié)給大家開個(gè)頭,詳細(xì)內(nèi)容可查看官方文檔PG109。

2023-07-10 10:43:18 630

630

原理圖s for the VIRTEX5MEZPWREV1Z 評(píng)估板

2023-07-07 19:59:21 0

0 本文介紹廣州星嵌DSP?C6657+Xilinx Zynq7035平臺(tái)下Xilinx Zynq7035算力指標(biāo)。

2023-07-07 14:15:01 681

681

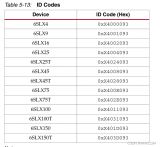

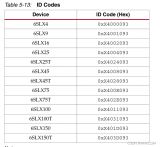

Xilinx任何一款FPGA型號(hào)都有一個(gè)唯一的IDCODE,用來區(qū)分不同的產(chǎn)品,同一型號(hào)不同封裝的FPGA IDCODE是一致的,可以通過JTAG、ICAP原語、AXI_HWICAP IP核等多種

2023-07-03 13:01:31 1580

1580

我做的一個(gè)基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個(gè)系統(tǒng),包括信號(hào)處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時(shí)鐘輸入為15MHz

2023-06-19 06:43:17

本文主要介紹說明XQ6657Z35-EVM 高速數(shù)據(jù)處理評(píng)估板ZYNQ(FPGA)與DSP之間GPIO通信的功能、使用步驟以及各個(gè)例程的運(yùn)行效果。1.1 ZYNQ與DSP之間GPIO通信1.1.1

2023-06-16 16:02:47

上文XILINX FPGA IP之Clocking Wizard詳解說到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過DRP進(jìn)行MMCM PLL的重新配置。

2023-06-12 18:24:03 5513

5513

鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過說明,但是對(duì)于fpga的應(yīng)用來說,使用Clocking Wizard IP時(shí)十分方便的。

2023-06-12 17:42:03 2883

2883

FPGA是一種可編程的,DSP是,當(dāng)系統(tǒng)設(shè)計(jì)人員在項(xiàng)目的架構(gòu)設(shè)計(jì)階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點(diǎn),然后再從內(nèi)部資源、編程語言、功能多個(gè)角度解析

2023-06-01 11:03:14

功能(如RAM、時(shí)鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個(gè)示意圖,實(shí)際上每一個(gè)系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出

2023-05-30 20:53:24

實(shí)驗(yàn)箱簡(jiǎn)介?基于TI TMS320F28335浮點(diǎn)DSP C28x + Xilinx Spartan-6 FPGA處理器,主頻為150MHz;?可拆式新型實(shí)驗(yàn)箱,使用靈活,性價(jià)比高。由核心板、實(shí)驗(yàn)

2023-05-29 09:48:57 2

2 Xilinx FPGA pcb設(shè)計(jì)

2023-05-29 09:11:36 0

0 Xilinx 7系列FPGA包含四個(gè)FPGA系列,可滿足整個(gè)系統(tǒng)要求,包括低成本,小尺寸,成本敏感的大批量應(yīng)用程序,可滿足最苛刻的超高端連接帶寬,邏輯容量和信號(hào)處理能力高性能的應(yīng)用程序。 7系列

2023-05-12 11:58:55 670

670 FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

廣州星嵌DSP/ARM/FPGA 選型手冊(cè)2023

2023-05-05 10:24:22 15

15 FPGA/CPLD的綜合、實(shí)現(xiàn)過程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析。

2023-04-27 10:08:22 768

768 VIRTEX5MEZPWREV1Z 用戶指南

2023-04-26 19:04:43 0

0 MIPI 接口現(xiàn)在非常流行,國產(chǎn)FPGA目前基本都帶MIPI接口,而AMD-Xilinx是從U+系列開始支持MIPI電平,從國內(nèi)使用情況來看,7系列FPGA是使用最廣的器件,所以這次使用的FPGA是7系列FPGA使用電阻網(wǎng)絡(luò)實(shí)現(xiàn)MIPI電平的例子。

2023-04-24 09:30:06 3704

3704

電力、儀器儀表、通信、醫(yī)療、安防等工業(yè)領(lǐng)域,與6大主流工業(yè)處理器原廠強(qiáng)強(qiáng)聯(lián)合,包括德州儀器(TI)、恩智浦(NXP)、賽靈思(Xilinx)、全志科技、瑞芯微、紫光同創(chuàng),產(chǎn)品架構(gòu)涵蓋ARM、FPGA、DSP、RISC-V等。 多樣廠商、多種架構(gòu)、國產(chǎn)?+?進(jìn)口,豐富了用戶的決策選擇,也

2023-04-14 13:10:02 816

816 、通信、醫(yī)療、安防等工業(yè)領(lǐng)域,與6大主流工業(yè)處理器原廠強(qiáng)強(qiáng)聯(lián)合,包括德州儀器(TI)、恩智浦(NXP)、賽靈思(Xilinx)、全志科技、瑞芯微、紫光同創(chuàng),產(chǎn)品架構(gòu)涵蓋ARM、FPGA、DSP

2023-03-31 16:19:06

評(píng)估板簡(jiǎn)介創(chuàng)龍科技 TL2837xF-EVM 是一款基于 TI C2000 系列 TMS320F2837xD 雙核 C28x 32 位浮點(diǎn) DSP + 紫光同創(chuàng) Logos/Xilinx

2023-03-31 15:30:13

不多說,上貨。Xilinx FPGA 開發(fā)流程及詳細(xì)說明本篇目錄1. 設(shè)計(jì)前準(zhǔn)備2. 建立工程3. 輸入設(shè)計(jì)4. 綜合分析5. RTL仿真6. 鎖定管腳7. 布局布線8. 生成配置文件并下載9.

2023-03-30 19:04:10

EVAL MODULE FOR XILINX FPGA

2023-03-30 11:56:16

EVAL MODULE FOR XILINX FPGA

2023-03-30 11:56:16

EVAL MODULE FOR XILINX FPGA

2023-03-30 11:51:24

KIT FOR VIRTEX ULTRASCLE FPGA

2023-03-30 11:49:31

VIRTEX-6 FPGA CONNECTIVITY KIT

2023-03-30 11:49:30

VIRTEX-6 FPGA CONNECTIVITY KIT

2023-03-30 11:49:30

VIRTEX-6 FPGA CONNECTIVITY KIT

2023-03-30 11:49:30

VIRTEX-6 FPGA CONNECTIVITY KIT

2023-03-30 11:49:30

VIRTEX-6 FAGAN ML605 EVAL KIT

2023-03-30 11:49:30

VIRTEX-6 FAGAN ML605 EVAL KIT

2023-03-30 11:49:24

總結(jié)Xilinx? FPGA 的上電模式可以分為以下4類型: 主模式 從模式 JTAG模式(調(diào)試模式) 系統(tǒng)模式(多片配置模式) 1、主模式 典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)

2023-03-29 14:50:06 533

533 Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

創(chuàng)龍科技最新、最全的ARM/FPGA/DSP嵌入式工業(yè)板卡選型大全2023.2版本正式發(fā)布了!十年磨一劍,接下來,一起來看看有哪些亮點(diǎn)~

2023-03-28 12:34:58 828

828 Xilinx LabTools工具是Xilinx FPGA單獨(dú)的編程和調(diào)試工具,是從ISE或Vivado中獨(dú)立出來的實(shí)驗(yàn)室工具,只能用來下載FPGA程序和進(jìn)行ILA調(diào)試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 4750

4750 創(chuàng)龍科技ARM/FPGA/DSP嵌入式板卡選型大全2023.2版本正式發(fā)布!接下來,跟著我們一起看看有哪些亮點(diǎn)吧!6大主流工業(yè)處理器原廠創(chuàng)龍科技現(xiàn)有30多條產(chǎn)品線,覆蓋工業(yè)自動(dòng)化、能源電力、儀器儀表

2023-03-24 15:38:21 1193

1193

支持所有Xilinx器件下載 包括FPGA CPLD ISP Configuration PROM 下載接口電壓:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論