Achronix首款22nm技術工藝FPGA誕生

2012年05月25日 11:38 來源:本站整理 作者:秩名 我要評論(0)

Achronix的高端視點:

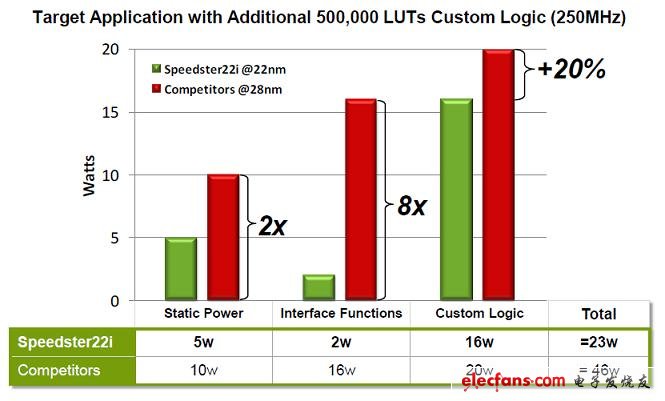

Speedster22i 功耗和成本僅為28nm高端FPGA的一半

Speedster22i 集成業界最好的、經芯片驗證過的硬核IP

Achronix的發展趨勢:

Speedster22i 有針對不同目標應用的兩個產品系列

提供強勁的第三代ACE設計工具

加強中國市場服務,提供全面的FAE支持

當Xilinx與Altera正在28nm節點相戰甚酣的時候,Achronix從半路殺出,宣布其首款22nm技術工藝 FPGA問世。在得到Intel最先進的22nm工藝生產線的首次開放代工之后, Achronix的Speedster22i 帶來了震撼性的驚喜:新22nmFPGA器件的功耗和成本只有28nm高端FPGA的一半。

日前, Achronix 半導體公司來華召開新聞發布會,公布了Speedster22i HD和HP產品系列的細節。其總裁兼首席執行官Robert Blake和中國區銷售總監羅煒亮(Eric Law)向電子元件技術網記者詳細介紹了產品的相關情況。

“Speedster22i FPGA產品是業內唯一針對應用的高端FPGA,功耗和成本均僅為28nm高端的FPGA的一半,且簡單易用,可顯著提高設計效率。” Robert Blake表示:“這些優勢得益于Achronix不尋常的策略:采用Intel領先的22nm FinFET工藝技術;針對特定市場通訊和測試方面的應用;并使用業界最好的硬核IP及輔助設計軟件。”

Robert Blake和Eric Law介紹Speedster22i是業界最高密度和最高性能的FPGA

功耗和成本僅為28nm高端FPGA的一半

“這種將英特爾22nm工藝的領先性,與我們在內核結構及面向目標應用的嵌入式硬IP這兩個方面的創新相結合,意味著我們的客戶將擁有一種高端的FPGA解決方案,其功耗和成本都為具有競爭性FPGA產品的一半。”Robert Blake介紹說。

對于目標應用,嵌入式硬核IP消耗的功率比在通用FPGA的可編程結構中執行相同功能要少90%。此外,由英特爾的22nm FinFET工藝所提供的創新可少耗達50%的功率,同時比構建在28nm平面工藝上的晶體管快接近40%。對于HD系列器件,這些因素結合在一起帶來了比主流FPGA低出最高可達50%的總功率消耗。

Speedster22i FPGA產品僅消耗28nm高端的FPGA一半的功率

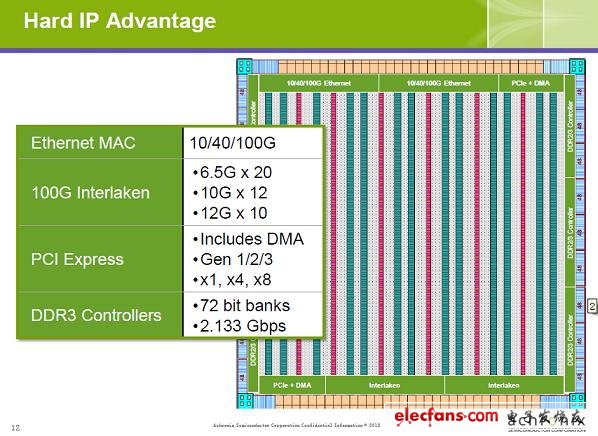

集成業界最好的、經芯片驗證過的硬核IP

“我們差異化戰略的一部分是集成同類中最佳的、經芯片驗證過的IP。” Achronix創始人兼董事長John Lofton Holt表示:“例如,除了英特爾22nm工藝所提供的巨大的功耗和性能優勢之外,我們的Speedster22i器件還充分發揮了一整套業界領先的I/O接口技術、核心技術的和由英特爾開發的封裝IP。這幫助我們獲得以前無法達到的性能和信號完整性新高度,并同時減少我們的開發時間和開發成本。”

Speedster22i器件中集成了同類中最佳的、經芯片驗證過的硬核IP

Speedster22i器件是首批包括內置端到端、硬核IP接口協議功能的FPGA,其硬核IP包括完整的I/O協議棧,可用于 10/40/100G、Interlaken、PCI Express gen1/2/3和用于2.133Gbps DDR3的內存控制器。在其他的FPGA中,這些功能都由可編程陣列來實現,使時序收斂具有挑戰性并要求占用可編程陣列中高達50萬個的等效查找表(LUT)。這給傳統的FPGA設計增加了大量的成本和功耗,而在Speedster FPGA產品中它們都是基本的連接。此外,嵌入式硬核IP消除了采購、集成和測試這些功能相應的軟核IP成本。

本文導航

- 第 1 頁:Achronix首款22nm技術工藝FPGA誕生(1)

- 第 2 頁:針對不同目標應用的兩個產品系列

上周熱點文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創新實用技術專題

熱評

- LM3S9B96開發板手冊及原理圖

- STM32F103ZET6紅牛電路圖

- 高通發布全新設計DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式漢化版免費下載

- hi3515海思原版原理圖

- matlab 7.0軟件下載(免費破解版)

- TX-1C型單片機開發板原理圖

- 三菱A500變頻器原理圖

- 三相IGBT全橋隔離驅動電源設計

博文

- 問什么郵箱激活不了

- 八成大學生認同先就業后擇業

- 我的心路

- 為什么郵箱激活不了

- 你是否曾這樣傷害過一個人?

- 2012.5.12 第一個DS18B20程序

- 到底有多少人在校園里浪費青春

- 到底有多少人在校園里浪費青春

- 藍牙技術越來越雞肋

- 【博客分享季】 我的單片機入門

用戶評論

查看全部 條評論

查看全部 條評論>>