如何應對電路板寄生組件對電路性能的干擾

電路板布線所產生主要寄生組件分別是電阻、電容以及電感。從電路圖轉成實際電路板時,所有寄生組件都有機會干擾電路性能。當一系統混合數字與模擬組件時,仔細布線是電路板成功與否關鍵。尤其,靠近高阻抗模擬走線經常變化之數字走線將造成嚴重耦合噪聲,只有讓這兩種走線保持距離方可避免這種現象。本文量化了最棘手電路板寄生組件、電路板電容,并列舉可清楚看到電路板上性能例子來說明。

非必要電容帶來困擾

兩條相鄰平行走線會形成布線電容。電容值可用(圖一)中所示公式計算。

注:兩條走線相鄰布置,即可在一塊電路板上形成電容。因為此種電容,在一條走在線快速電壓變化可在另一條走在線引起電流信號。

圖一 兩條走線相鄰布置可在一塊電路板上形成電容

當高阻抗模擬走線貼近數字走線時,這種電容可能會在敏感混合訊號電路中造成問題。例如 (圖二)中電路就可能會面臨這類問題。

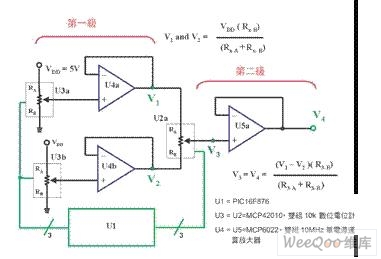

注:以三個8位數字電位計和三個運算放大器組成之輸出電壓達 6萬5536階之16位數字模擬轉換器。如果 VDD 在這個系統內是 5V,這個數字模擬轉換器分辨率或 LSB大小就是 76.3μV。

圖二 線與線太靠近,容易在電路板中產生寄生電容

(圖二)電路動作,使用三個8位數字電位計和三個CMOS運算放大器來組成一個16位數字模擬轉換器。圖二左側,有兩個數位電位計(U3a and U3b)接到 VDD與地間,該中心抽頭輸出端連接至兩個運算放大器(U4a 與 U4b)非反向輸入端。使用微控制器U1 之SPI接口來規劃數字電位計U2與U3。在這個架構中,每個數字電位計被規劃為一個8位之多階數字模擬轉換器。如果VDD等于5V,這些數字模擬轉換器 LSB 大小等于19.61mV。

這兩個數字電位計之中心抽頭端被連接至兩個當緩沖器運算放大器之非反向輸入端。在這個電路結構中,運算放大器之輸入端是高阻抗,將數字電位計與電路其它部份隔離。這兩個運算放大器輸出之變化振幅被規劃在不會超出第二級運算放大器允許范圍內。

要讓這個電路形成16位數字模擬轉換器(U2a),第三個數字電位計會在這兩個運算放大器U4a與U4b之輸出范圍內變動。規劃U3a和U3b用來設定數字電位計之輸出電壓。再者,如果VDD是5V,則有可能將U3a與U3b個別規劃為每一步19.61mV變化量。以此電壓跨在第三個8位數字電位計R3 上,使本電路最低有效位所對應電壓值為 76.3uV。

本電路可被用于兩種基本操作模式;第一種模式用于可規劃調整之直流參考電壓,在這個模式中,只是偶爾使用電路之數字部份而在正常操作中卻沒有;第二種模式用于任意波型產生器,在這個模式中,電路之數字部份是操作核心,且可能發生電容耦合情形。圖二中電路第一種完成布線如(圖三)所示。

注:此為對圖二中電路第一種布線。在圖二中可迅速看到,重要高阻抗模擬走線與數字走線極為接近。本結構在模擬走在線,因特定數位走線之數據輸入碼改變,產生無預期且隨數字電位計規劃需求而變化噪聲。

圖三 圖二中另一方式布線圖

觀察布線中有顏色走線,潛在問題很明顯。箭頭所指模擬走線(藍色)從U3a之中心抽頭至U4a之高阻抗放大器輸入端。另一箭頭所指數字走線(綠色)是用來傳送數字數據以規劃設定數字電位計。在實驗桌上,發現綠色走在線數字訊號耦合到敏感藍色走線內,如(圖四)所示。

注:示波器照片中,最上面是JP1波形(規劃數字電位計數字數據),中間是JP5波形(在相鄰模擬走在線噪聲),最下面$是TP10波形(16位數字模擬轉換器輸出端噪聲)

圖四 示波器照片圖

在系統中,規劃數字電位計之數字訊號已從走線感應到到另一條具有直流電壓之模擬走線,而這個噪聲又一路透過電路模擬部份傳遞到第三數字電位計(U5a)。第三數字電位計在兩個運算放大器之輸出狀態間變動。解決該問題之方式為將走線分開。(圖五)顯示一個改善布線解決方案。

注:這個距離實質上已消除了在之前布線中造成干擾數字噪聲。

圖五 使用這個新布線,模擬走線和數字走線已被分開

注:這個新布線中16位數字模擬轉換器正顯示一個單*轉換,從通信到數字電位計沒有任何數字噪聲。

布線變更結果將模擬與數字走線仔細分開,本電路變成一個很干凈16位數字模擬轉換器。第三數字電位計76.29μV一個單*轉換顯示在綠色波形。示波器刻度是80mV/div且被顯示代碼變更幅度約為80mV。受限于實究室配備,所以將 16位數字模擬轉換器輸出乘以1000倍。