導 讀

雖然,所有以指數規律增長的曲線在物理意義上均是不可持續的,摩爾定律正是如此。 然而,人們卻一直想方設法地去延續摩爾定律,為什么明知不可為而為之?這其實代表了人類的一種理想主義,這種理想或信念往往讓人類超越自身,創造出意想不到的科技和文明。 或許正是人們相信了摩爾定律的可持續性,從而帶來的信念推動了集成電路五十多年的高速發展。摩爾定律剛提出的時候,我想摩爾本人也不相信在不到芝麻粒大小的一平方毫米,可以集成超過一億只以上的晶體管。 今天,在指甲蓋大小的芯片上,集成的晶體管數量超過了100億,還可以再多嗎?答案依然是肯定的。 然而,隨著芯片特征尺寸日益走向極致(3nm~1nm),集成電路中晶體管尺寸的微縮逐漸接近硅原子的物理極限。1nm的寬度中僅能容納2個硅原子晶格(a=0.5nm),也就是說,在單晶硅中,3個硅原子并排排列的寬度就達到了1nm。 下一步,集成電路技術會走向何方呢?在本文中,您或許能找到自己的答案。

01

更多的晶體管?

現代科技的發展是以集成電路為基石。集成電路發展的最直接的目標就是在單位面積內或者單位體積內集成更多的晶體管。因此,集成電路的第一個發展方向就是集成更多的晶體管。

單位面積內更多的晶體管? ? ?

在單位面積內集成更多的晶體管就需要將晶體管做的更小,幾十年來,在摩爾定律的推動下,晶體管的特征尺寸從毫米級到微米級再到納米級,尺寸縮小了百萬倍。今天,在一平方毫米內可集成超過上億的晶體管,芯片上的晶體管數量已經達到百億量級。

在單位面積內集成更多的晶體管

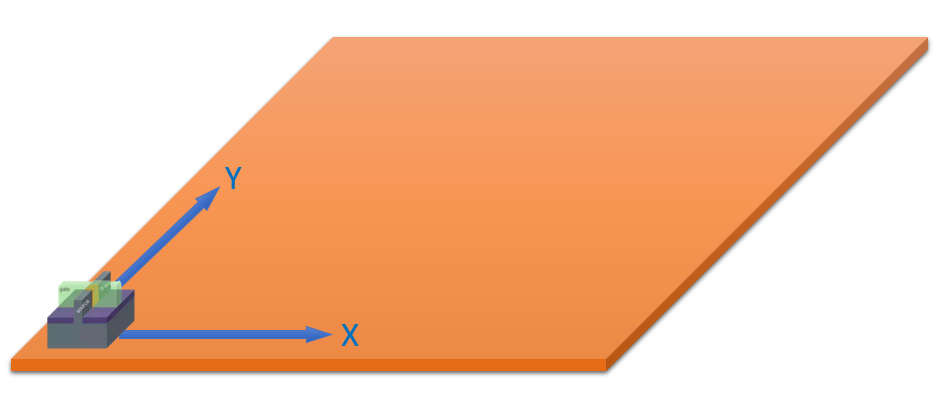

那么,晶體管能小到什么程度呢?大致受兩個因素的制約,一個是晶體管內最小的結構寬度,另一個是晶體管自身所占的面積。 晶體管的最小的結構寬度在22nm之前,通常是柵極寬度,被稱為特征尺寸。隨著晶體管面積的日益縮小,特征尺寸和廠家的命名逐漸脫節,而柵極寬度也不再是晶體管的最小結構寬度,例如在FinFET中,Fin的寬度通常是小于柵極寬度的,在GAA堆疊納米片晶體管中,納米片的厚度也是要小于柵極寬度的。

因此,各大Foundry不再以柵極寬度作為晶體管的特征尺寸,其工藝節點成為一個代名詞,并不和某個特定的寬度相對應,但依然是有其物理意義的。主要體現在晶體管面積的縮小,在同樣的面積內可集成更多的晶體管。

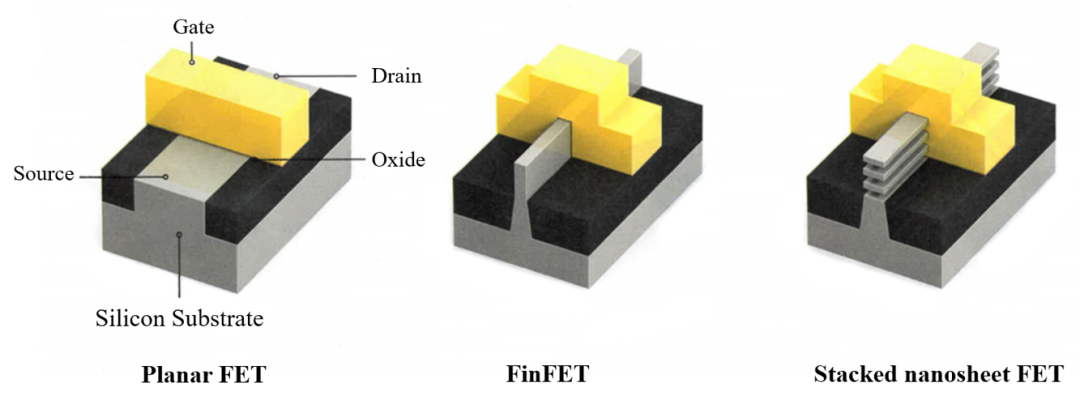

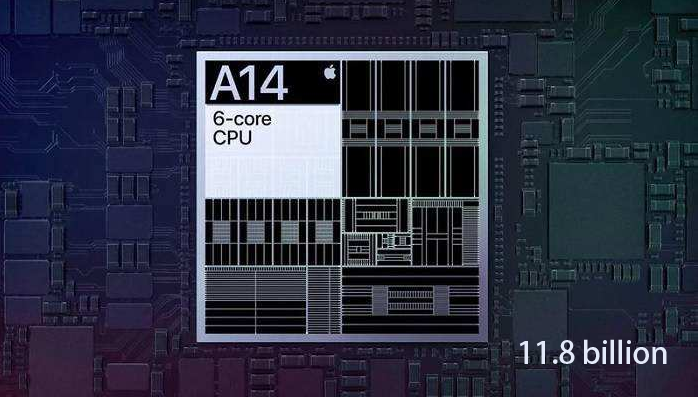

例如,蘋果A13芯片采用7nm工藝制程,內有85億個晶體管,其面積為94.48平方毫米,在1平方毫米可集成8997萬個晶體管:0.8997億/mm^2。蘋果A14芯片采用5nm工藝制程,內有118億個晶體管,其面積為88平方毫米,在1平方毫米可集成1.34億個晶體管:1.34億/mm^2

兩者的晶體管平均面積之比為1.49,如果嚴格按照7:5的比值為1.4,其平方為1.96,可以看出,相對于7納米芯片,5納米芯片做到了理論值的76%。這也是intel一直認為別的Foundry廠家的命名有水分的原因。

從平面晶體管到FinFET到GAA,晶體管的尺寸不斷縮小,結構不斷優化,就是為了在單位面積內集成更多的晶體管。

?

單位體積內更多的晶體管? ? ?

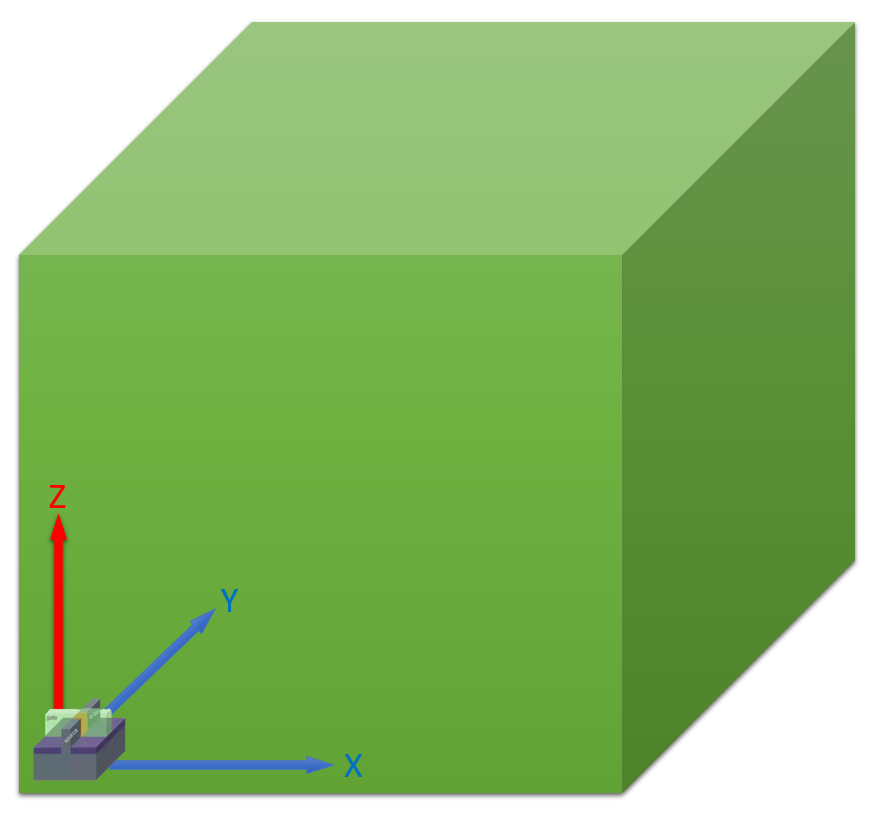

而在單位體積內集成更多的晶體管,除了可以將晶體管做的更小之外,還因為多了一個空間維度,因此可以將晶體管堆疊起來。

在單位體積內集成更多的晶體管

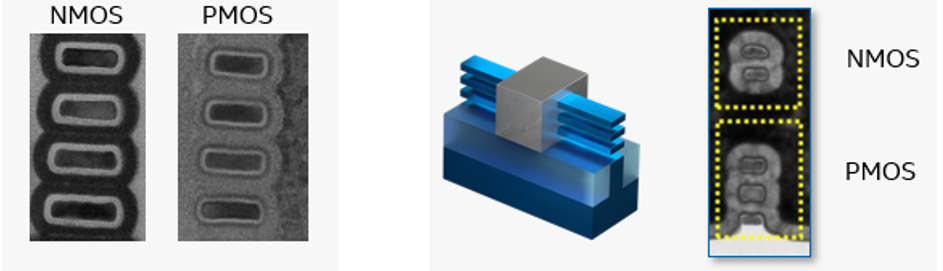

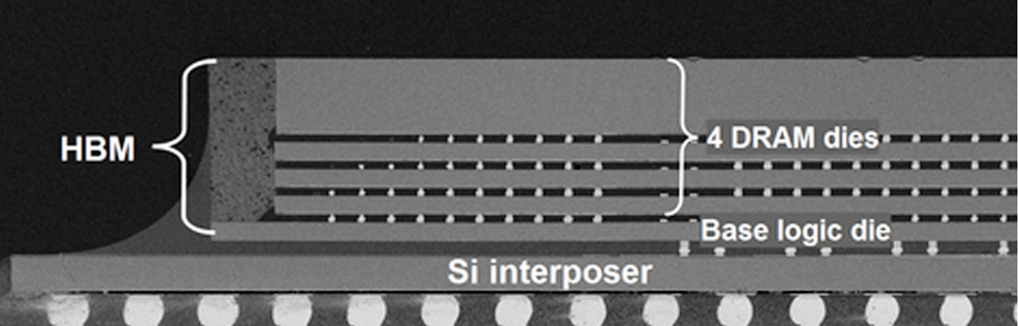

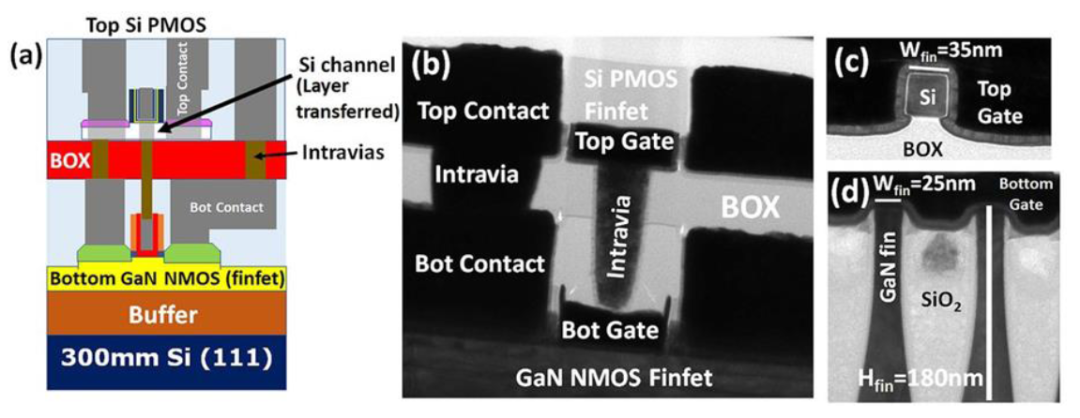

如何進行晶體管的堆疊呢? 大致兩種方法,第一種就是在晶圓上通過特殊工藝將晶體管直接做成多層的;另外一種就是和傳統工藝相同的方法在晶圓上制作一層晶體管,然后將多個晶圓堆疊起來,晶圓之間通過TSV連接。 關于第一種方法,目前有很多研究,例如將NMOS堆疊在PMOS上,從而節省一半的面積,使晶體管密度提升一倍。其難點在于上層的晶體管沒有致密的硅基底作為支撐,很難制作出高質量的晶體管,另外,目前的技術也只能支持兩層堆疊。

第二種方法目前應用如火如荼,通常被稱之為先進封裝技術(Advanced Packaging)。 先進封裝也稱為HDAP高密度先進封裝,目前受關注度很高,技術發展迅速,晶圓間互連的TSV密度越來越高,并且理論上不受堆疊層數的限制,最先進的技術目前掌握在Foundry手中。

不過,現在Foundry廠逐漸不把其作為封裝技術來看待,而將其視為晶圓制造的一個重要環節,例如TSMC,在其產品線種將其定義為3D Fabric。 理論上講,XYZ三個維度并沒有本質不同,因此,增加一個維度,其集成的晶體管數量可能會成千上萬倍地增加,這也被很多人認為摩爾定律可持續的重要原因。 在集成電路中,晶體管作為最小的功能單位,我們可以稱之為功能細胞。在單位體積內集成更多的功能細胞,即提升系統的功能密度。 從歷史來看,在所有的人造系統中,功能密度都在不斷地提升,雖然不同的歷史階段提升的有快有慢,但在人類文明發展的進程中不會停滯。

02

擴展硅元素?

雖然化合物半導體近來比較熱門,但集成電路中,硅目前還是占據著絕對的主流位置。因此,芯片制造商一直試圖將化合物半導體應用在傳統的硅晶圓上,從而有效利用現有資源并創造出更大的經濟效益。

?

硅基氮化鎵技術? ? ?

通過在300毫米的硅晶圓上集成氮化鎵基(GaN-based)功率器件與硅基CMOS,實現了更高效的電源技術。這為CPU提供低損耗、高速電能傳輸創造了條件,同時也減少了主板組件和空間。 氮化鎵半導體器件主要可分為GaN-on-Si(硅基氮化鎵)、GaN-on-SiC(碳化硅基氮化鎵),GaN-on-sapphire(藍寶石基氮化鎵)等幾種晶圓。 由于成本和技術等因素,硅基氮化鎵成為了目前半導體市場主流。 英特爾在300毫米的硅晶圓上首次集成氮化鎵基(GaN-based)功率器件,此研究驗證了300毫米工藝兼容可行性,更適配高電壓應用,增加了功能,提升了大規模制造可能性。

全世界現在大概有上萬億美元的投資都是在300毫米硅晶圓設備、生態系統上,需要把這些充分利用起來,這樣制造成本才能下降。 此外,臺積電目前采用的也是GaN-on-Si(硅基氮化鎵)技術。

?

新型鐵電體材料 ? ??

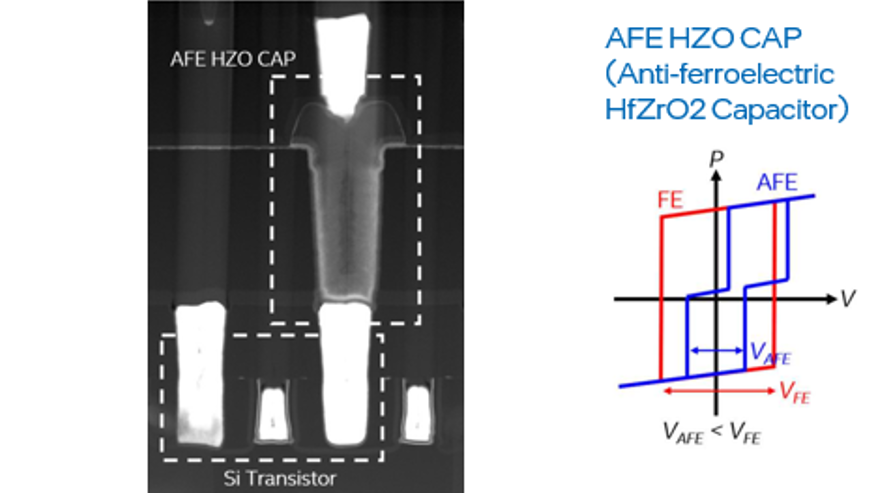

另一項技術是利用新型鐵電體材料作為下一代嵌入式DRAM技術的可行方案。該項技術可提供更大內存資源和低時延讀寫能力,用于解決從人工智能到高性能計算等應用所面臨的日益復雜的問題。 新型鐵電存儲器,采用新的技術實現了2納秒的讀寫速度和超過10的12次方的讀寫周期,其性能和壽命都遠超現有的存儲器。

鐵電存儲器可以和傳統的CMOS工藝結合,用來作為從L1 Cache到DRMA之間的中間層。 擴展硅元素,在功率器件和內存增益領域提升硅基半導體的性能,目前已經取得了不錯的進展。人們還在不斷地努力探尋其它的方法來擴展硅元素。 ?

03

探尋量子領域?

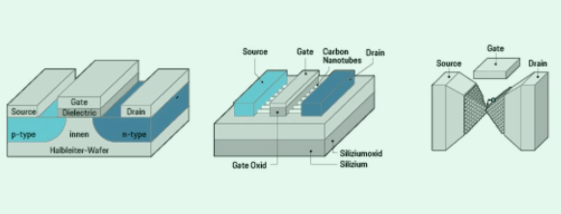

由于量子力學隧道效應,電子可以穿越絕緣體,這將使元件功能失效。人們開始尋找一種新型晶體管,可以進一步提高未來集成電路的性能,作為傳統晶體管的替代品。目前有很多研究,但還沒有領先者可以取代硅MOSFET。 研究人員列出了一系列MOSFET替代品,包括隧道場效應晶體管TFET,碳納米管場效應晶體管,單原子晶體管。

?

隧道場效應晶體管 ? ??

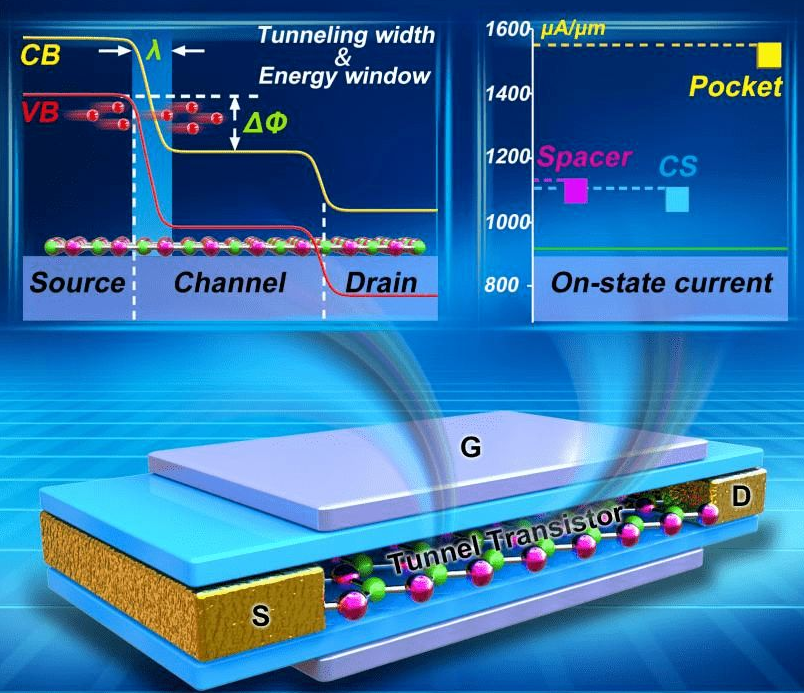

隧道場效應晶體管(TFET-Tunnel Field Effect Transistor),和傳統MOSFET晶體管原理不同,在TFET中源極和漏極摻雜不同。它使用量子力學隧道效應,柵極和源極之間的電壓決定了電荷載流子是否可以“隧穿”通過源極和漏極之間的能量勢壘,以及電流是否可能流動。

根據量子理論,有些電子縱使明顯缺乏足夠的能量來穿過能量勢壘,它們也能做到這一點,這就是量子隧道效應。

在隧道場效應晶體管中,兩個小槽被一個能量勢壘分開。在第一個小槽中,一大群電子在靜靜等待著,晶體管沒有被激活,當施加電壓時,電子就會通過能量勢壘并且移入第二個小槽內,同時激活晶體管。TFET在結構上類似于傳統晶體管,但在開關方面利用了量子力學隧道效應,既節能又快捷。

通過減少能量勢壘的幅度,增強并利用量子效應將成為可能,因此,電子穿過勢壘所需要的能量會大大減少,晶體管的能耗也會因此而顯著下降。利用量子隧道效應研制出的隧道場效應晶體管有望將芯片的能耗減少到百分之一(1/100)。

?

碳納米管場效應晶體管?? ??

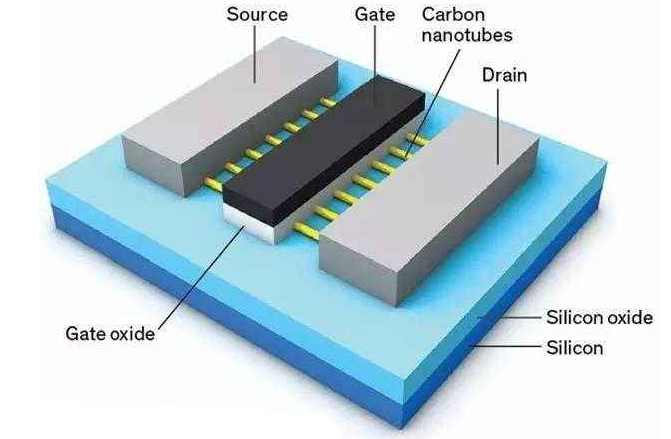

碳納米管場效應晶體管(CNFET-Carbon?Nanotube Field Effect Transistor)

在CNFET中,源極和漏極之間的溝道由碳納米管組成,其直徑僅有1–3 nm, 意味著其作為晶體管的溝道更容易被柵控制。因此, 碳納米管晶體管比傳統硅基晶體管在比例縮減上的潛力會更大。

碳納米管具有超高的室溫載流子遷移率和飽和速度,室溫下,碳納米管中載流子遷移率大約為硅的100倍, 飽和速度大約是硅的4倍。在相同溝道長度下, 載流子遷移率越高,飽和速度越高,速度越快,并能增加能量的利用效率。

碳納米管晶體管具備超低電壓驅動的潛力,從而在低功耗方面具有巨大優勢,在溝道材料的選擇中, 碳納米管溝道同時具備了天然小尺寸、更好的尺寸縮減潛力和低功耗等關鍵因素。

?

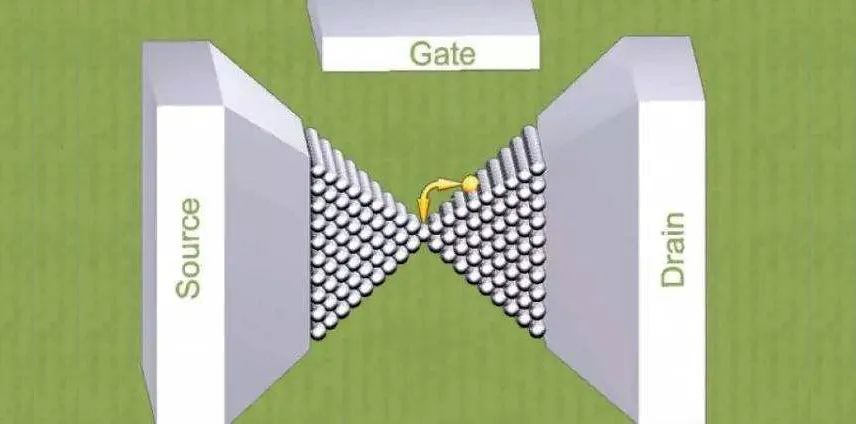

單原子晶體管?? ??

單原子晶體管(Single-Atom Transistor),在這種晶體管中,控制電極移動一個原子,該原子可以連接兩端之間的微小間隙,從而使電流能夠流動。原則上,它的工作原理就像一個有兩個穩定狀態的繼電器。

在單原子晶體管中,通過源極和柵極之間的電壓移動單個原子,從而關閉或打開源極和漏極之間的電路。

在只有單一金屬原子寬度的縫隙間建立微小的金屬觸點,實現目前晶體管所能達到的最小極限。在此縫隙通過電控脈沖移動單個原子,完成電路閉合,將該原子移出縫隙,電路被切斷。

由此實現世界上最小晶體管在接通電源情況下單個原子的受控可逆運動。 單原子晶體管由金屬構成,不含半導體材料,所需電壓極低,能耗也極低。據稱,單原子晶體管的能耗將只有傳統硅基晶體管的萬分之一(1/10000)。 與傳統量子電子元件不同,單原子晶體管不需要在接近絕對零度的低溫條件工作,它可以在室溫下工作,這對未來應用是一個決定性的優勢。 ?

總 結

這篇文章源于2021年末英特爾的一次媒體技術解讀會,在這次會議中,英特爾副總裁盧東輝博士詳細解讀了Intel在IEDM 2021上發布的三個關鍵領域的技術突破。 這次媒體技術解讀會之后,我對其中涉及的技術點進行了詳細的分析并進行了一定的擴展,從intel所取得的技術突破,擴展到了整個行業的技術發展方向。 更多的晶體管,擴展硅元素,探尋量子領域,是集成電路技術發展的三大方向。 目前看來,最切合實際的發展方向還是更多的晶體管,我們可以將其定為近期的目標,而其他兩項則可以看做相對長遠的目標。 如何實現更多的晶體管,推薦大家參考上面這本厚厚的新書,相信會有更多的收獲!

審核編輯 :李倩

?