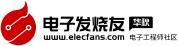

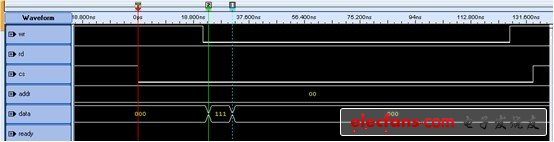

寫(xiě)HPID 的時(shí)序截圖如下:

兩個(gè)時(shí)序圖顯示主機(jī)送出的數(shù)據(jù)111b 在HSTROBE(ARM_WR)的下降沿后,很快被改變成其它值000b。在寫(xiě)HPID 的時(shí)序截圖中,第一個(gè)HSTROBE 的下降后,HPI 送出HRDY 信號(hào),然后數(shù)據(jù)線被改變,首先判斷HPI 對(duì)主機(jī)的命令做出了響應(yīng),通過(guò)HRDY 信號(hào)的出現(xiàn)時(shí)機(jī),說(shuō)明HPI 判斷這是一個(gè)讀操作,可以判斷為HSTROBE 的下降沿采樣HR/W信號(hào)不正確。

從硬件連接來(lái)看,HSTROBE(HR/W)要采樣HR/W,HCNTL0/1 來(lái)判斷主機(jī)命令, HR/W的與HSTROBE 為同一信號(hào)源,且同為下降沿,HR/W與HSTROBE 的下降沿之間的setup 時(shí)間不夠,采樣HR/W的電平狀態(tài)出現(xiàn)誤判,認(rèn)為是高電平讀命令,HPI 對(duì)讀命令的響應(yīng)則是在第一個(gè)HSTROBE 的下降沿之后送出HRDY 信號(hào),并在HRDY 之后,HPI 送出數(shù)據(jù)到總線上。

對(duì)于該問(wèn)題,需要對(duì)參與HSTROBE 邏輯譯碼的HR/W信號(hào)的下降沿做延時(shí)處理,可在邏輯電路如CPLD 或 FPGA 里實(shí)現(xiàn),以確保HSTROBE 的下降沿采樣到穩(wěn)定的HR/W電平。

?

1.2讀數(shù)據(jù)不正確

通常表現(xiàn)為讀讀HPIC,HPIA 正常,但讀HPID 不正常,前半字為0,后半字正確,對(duì)同一個(gè)地址讀兩次,第二次的數(shù)據(jù)完全正確。

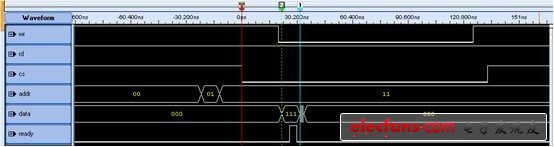

在案例中,用示波器觀察HCS 與HRDY 之間的時(shí)序關(guān)系,發(fā)現(xiàn)HCS 的上升沿在HRDY 的上升沿之前,即主機(jī)在HPI 數(shù)據(jù)有效之前結(jié)束了訪問(wèn)周期。HRDY 的上升沿其實(shí)是因?yàn)镠CS 的結(jié)束而拉高的,并非數(shù)據(jù)真正有效。

用戶由于沒(méi)有在硬件上將HRDY 與主機(jī)PowerPC 的TA 信號(hào)互連,沒(méi)有硬件握手機(jī)制,于是從軟件配置上加大主機(jī)的總線訪問(wèn)周期,即增加HCS 的寬度,故障現(xiàn)象沒(méi)有變化。

原因分析:讀HPID 與HPIC,HPIA 時(shí)序不同,讀HPID 操作需要HPI DMA 從HPIA 所指向的地址讀數(shù)據(jù)到 HPID,會(huì)有時(shí)間上的延時(shí)。而讀HPIC 和HPIA 直接從寄存器讀數(shù)據(jù),沒(méi)有延時(shí),所以讀HPIC,HPIA 是正確的。在讀HPID 時(shí),HPI 會(huì)在第一個(gè)HSTROBE 的下降沿后將HRDY 置位,指示數(shù)據(jù)未準(zhǔn)備好的忙狀態(tài),主機(jī)應(yīng)當(dāng)在總線上插入等待周期,數(shù)據(jù)準(zhǔn)備好后HPI 清除HRDY,主機(jī)才可以結(jié)束總線周期,通過(guò)HCS 的上升沿將有效數(shù)據(jù)鎖存。

HSTROBE 的下降沿到數(shù)據(jù)有效之間的延時(shí)與芯片及HPI 接口的工作頻率相關(guān),以C5502,C5501 為例,在芯片手冊(cè)中,這個(gè)延時(shí)參數(shù)H1 在SYSCLK1 與CPU 時(shí)鐘的分頻為4 時(shí),最大延時(shí)為12*2H+20(ns),H=SYSCLK1/2,在HPI 啟動(dòng)期間,PLL 沒(méi)有倍頻,處于旁通狀態(tài),系統(tǒng)輸入時(shí)鐘就是CPU 的工作時(shí)鐘,SYSCLK1默認(rèn)分頻為CPU 時(shí)鐘的4 分頻,以輸入時(shí)鐘為25MHz 為例,最大延時(shí)為:

這個(gè)時(shí)間長(zhǎng)度通常超出了主機(jī)端總線周期的軟件配置范圍,所以通過(guò)軟件配置增加HCS 的寬度不一定能滿足 HRDY 的最大延時(shí)要求。在有的DSP 芯片手冊(cè)上只提供了HRDY 的最小延時(shí),最大延時(shí)與芯片的優(yōu)先級(jí)設(shè)置,及系統(tǒng)配置相關(guān)而不確定,比如與系統(tǒng)中其它主模塊如EDMA 同時(shí)訪問(wèn)DDR,那么延時(shí)與HPI 的優(yōu)先級(jí),EDMA 的優(yōu)先級(jí),EDMA 的burst 長(zhǎng)度,以及DDR 的命令排序等配置相關(guān),這樣通過(guò)延長(zhǎng)主機(jī)的總線訪問(wèn)周期,更加不可靠。

解決辦法:在硬件設(shè)計(jì)之初,一定要利用HRDY 硬件握手信號(hào)[2][3]。雖然有的芯片HPIC 寄存器提供了HRDY 軟件握手方式,只能做為彌補(bǔ)硬件設(shè)計(jì)之初遺漏HRDY 硬件握手信號(hào)的權(quán)宜之計(jì),軟件輪循HRDY 的辦法會(huì)帶來(lái)額外的開(kāi)銷,降低HPI 總線的吞吐率,增加主機(jī)軟件實(shí)現(xiàn)的復(fù)雜度。而且有的芯片HPI 不支持HRDY 軟件查詢方法,只能通過(guò)硬件HRDY 保證數(shù)據(jù)的有效性。

?