現(xiàn)代的電子裝置設計須提供多個不同的直流(DC)電壓,導致內部電路須透過升壓與降壓方式轉換電壓,為裝置中負責不同功能單元供電;其中,在高效率DC-DC電源轉換設計方面,以電感為基礎的轉換拓撲,以及應用于各種開關的金屬氧化物半導體場效電晶體(MOSFET)已變得相當重要。

電感拓撲改善DC-DC轉換效率

以新一代小訊號MOSFET為例,具有低汲極(Drain)/源極(Source)導通電阻(RDSon)和良好的開關性能,并采用小型扁平封裝,開啟中功率開關模式DC-DC轉換的應用新領域。儘管高效率電源亦可采用整合型方案,但系統(tǒng)廠考量設計靈活性和成本,仍廣泛使用外部功率開關。

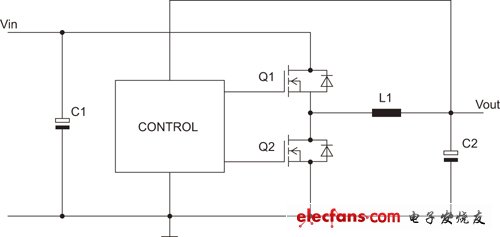

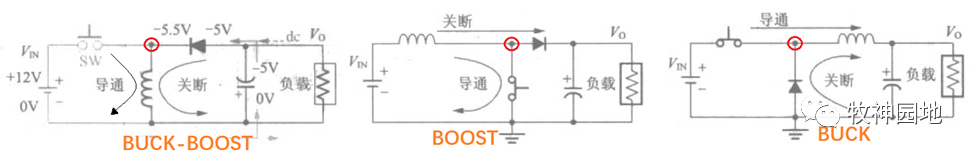

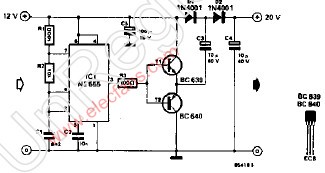

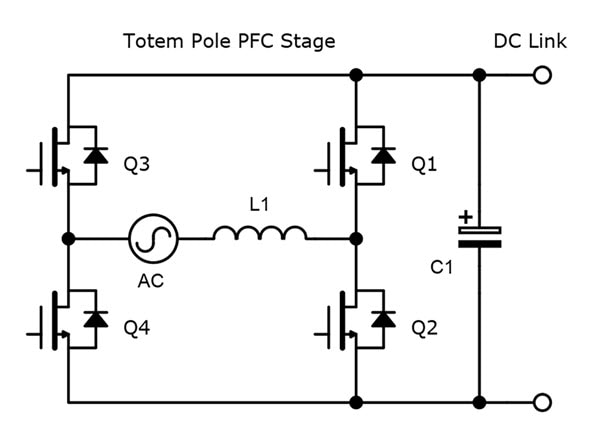

由于電荷幫浦等應用常受到低電流的限制,對高輸出功率和高效率電壓轉換器而言,最佳解決方案是采用電感拓撲,只須稍加改動便可實現(xiàn)升壓、降壓或升降壓轉換器。圖1是一個簡單的DC-DC降壓轉換器電路圖,相較于線性穩(wěn)壓器,該電路在理想元件應用中具有100%的轉換效能;不過,導通電阻不等于0歐姆(Ω),且電晶體開關將產(chǎn)生損耗與花費時間,電感因具有來自繞組導線的歐姆電阻,其磁芯也會增加損耗。

圖1 DC-DC降壓轉換器架構圖

磁芯損耗係來自磁場變化引起小磁域運動而造成的,核心材料的遲滯愈厲害,損耗相對提高;另渦流也會導致電感磁芯損耗,因磁場變化將形成電流環(huán)路,使鐵磁性材料變熱。對高頻開關來說,線路上的電流不再占據(jù)整個線路截面,反而偏向于貼近線路表面,這就是著名的集膚效應(Skin Effect),將增大電阻損耗。

此外,輸出電容具有剩余電阻,也會導致電能損耗和溫度上升,因二極體(Diode)最終會產(chǎn)生正向電壓損耗和反向電流損耗。在現(xiàn)實條件下,這些機制與實際情況會使DC-DC轉換器效率降至75?98%之間。

模擬與實作高效率DC-DC降壓設計

以圖1的DC-DC降壓設計為例,Q1為P通道MOSFET,做為高端開關用途,當MOSFET開啟時,L1電感上的電流線性增大:ΔIL=(ton/L1)×(VIN×VOUT)。假設VOUT恆定,開關打開時,電流持續(xù)流經(jīng)二極體D1,當正向電壓VF對地時,D1陰極為負,電流以線性方式下降,C2緩衝輸出電壓值愈大,漣波愈小。

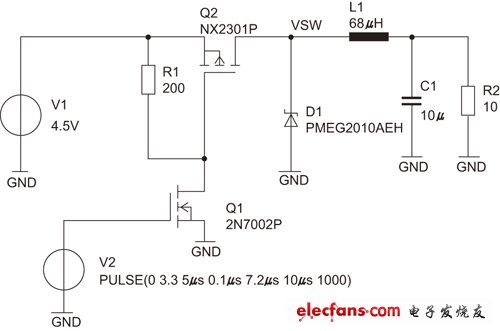

圖2則表示SPICE(Simulation Program with Integrated Circuit Emphasis)模擬,高端開關整合P通道MOSFET,電源V1對其供電,電感值則選定為68μH,輸出電壓采用10μF電容進行濾波;蕭特基二極體(Schottky Diode)D1做為續(xù)流二極體。此外,N通道驅動器MOSFET Q2則透過3.3伏特(V)高位準(V2)方波發(fā)生器,從而實現(xiàn)開關動作。本例中,開關頻率為100kHz,并在輸出端連接一個10歐姆的負載電阻。

圖2 DC-DC降壓轉換器SPICE模擬圖

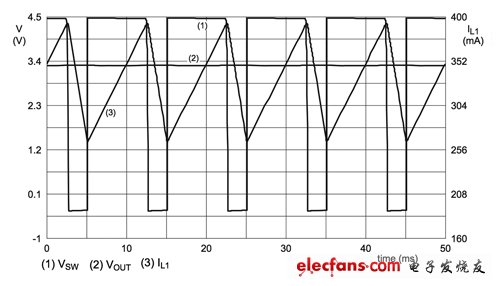

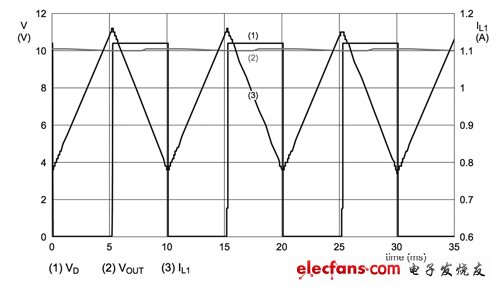

圖3係模擬結果,當Q1開啟時,流經(jīng)電感的電流IL1表現(xiàn)出線性增大,開關節(jié)點電壓VSW幾乎等于輸入電壓;當Q1關閉時,流經(jīng)電感的電流下降,開關號轉為300毫伏特負電壓,即蕭特基二極體的正向電壓,輸出電流為叁角波形的平均值,約為330毫安培(mA),輸出電壓VOUT在大約3.25伏特處保持穩(wěn)定。

圖3 DC-DC降壓轉換器電流、開關節(jié)點及輸出電壓模擬數(shù)據(jù)

該例中,電流在整個開關週期內流經(jīng)電感,這種模式稱為DC-DC轉換器的持續(xù)模式,輸出電壓計算公式如公式1、2;電感電壓計算方法如公式3:

VL=L×(dIL/dt)。。。。。。(1)

VL=L×(ΔIL/Δt)。。。。。。(2)

ΔIL=VL/L×Δt.。。。。。(3)

電感儲存的電量則以公式4表示:

E=L/2×I2.。。。。。(4)

對于開關關閉時的靜態(tài)模式而言,電感增加的電量須等于開關打開時損耗的電量,忽略開關和二極體正向電壓的RDSon損耗,即可得出計算ΔIL的公式5:

ΔIL=VIN–VOUT)×ton=VOUT×toff

VOUT/VIN=ton/(ton+toff)= ton/T.。。。。。(5)

其中,T為週期時間,工作週期為D=ton/T、VOUT=VIN×D;本例中,VOUT= 4.5V×(7.2/10)=3.24V。極端情況下,若工作週期為1,則開關始終關閉且輸出電壓等于輸入電壓;工作週期小于1,則輸出電壓的下降多少取決于工作週期係數(shù)D。

此時,電流漣波如公式6所示:

ΔIL=(VIN–VOUT)/L×ton.。。。。。(6)

本例的數(shù)值為ΔIL=(4.5V–3.24V)/ 68μH×7.2μs=133mA。

電感拓撲可輕易變換升/降壓設計

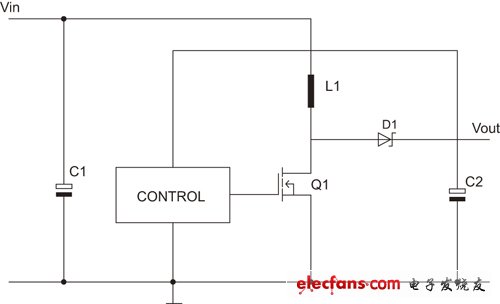

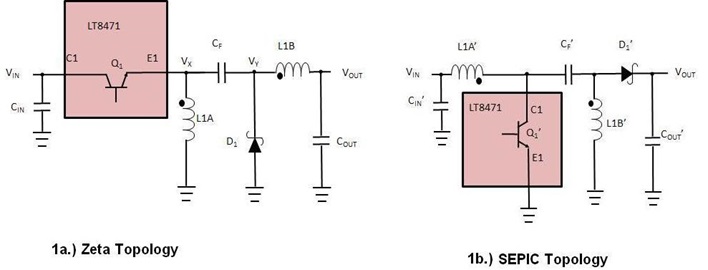

事實上,以電感為基礎的DC-DC降壓轉換器,只須稍為更改拓撲結構,降壓轉換器亦可成為升壓轉換器。如圖4為一個簡單的DC-DC升壓轉換器拓撲,若低端MOSFET Q1關閉,則電感上的電流會增大,可由公式7計算:

圖4 DC-DC升壓轉換器架構圖

ΔIL=VIN×ton.。。。。。(7)

由于陽極接地且陰極連接至C2的正電壓VOUT,二極體D1以反相模式驅動,若開關關閉,則電流IL繼續(xù)流經(jīng)D1至輸出;若轉換器在靜態(tài)模式下工作,則可根據(jù)公式8、9、10計算:

ΔIL=VIN/L×ton=(VOUT–VIN)/L×toff.。。(8)

VIN×ton=(VOUT–VIN)×toff 。。。。。(9)

VOUT=VIN×(ton/toff+1)。。。。。。(10)

工作週期為D=ton/T;T=ton+toff。

等式的極端情況表示當D=0,即電晶體從未開啟時,輸出電壓等于輸入電壓。這時須考慮無損耗元件,意味著二極體無正向電壓,且電感無繞組歐姆電阻和先前討論的額外損耗機制。若D接近1,則輸出電壓將快速上升,這對于安全運行將有重大影響,因為高工作週期會造成MOSFET汲極電壓偏高。

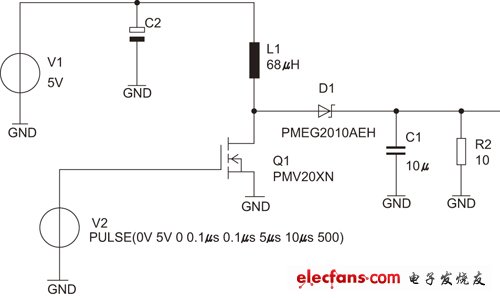

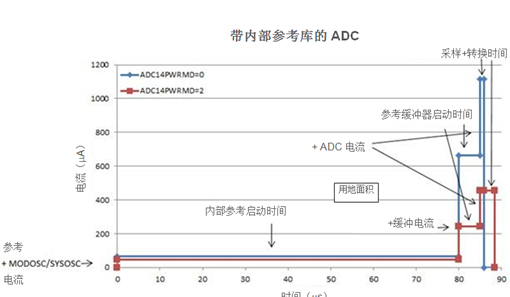

圖5表示SPICE模擬,低端開關整合采用SOT23封裝的N通道MOSFET及蕭特基二極體,轉換器開關采用100kHz控制訊號,工作週期為0.5。至于圖6表示模擬結果,其中的曲線2代表輸出電壓,對理想元件而言,由于工作週期為0.5,輸出電壓將等于輸入的兩倍。

圖5 DC-DC升壓轉換器SPICE模擬圖

圖6 DC-DC升壓轉換器電流、電壓模擬數(shù)據(jù)

實際上,二極體的正向電壓會降低輸出電壓,曲線1表示N通道MOSFET的汲極電壓VD,其在接地電壓和VD(最大值)之間切換,可由公式11表示:

VD(max)=VIN×1/(1–D)+VF 。。。(11)

在本模擬案例中,工作週期D=0.5,VD(max)=2×VIN+VF。

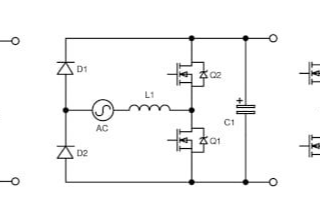

小訊號MOSFET提高電路轉換效率

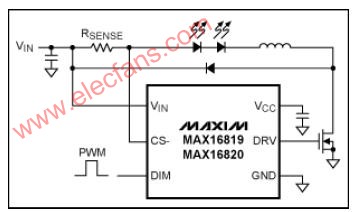

類似DC-DC降壓轉換器的設計,若將蕭特基二極體替換為MOSFET,同樣可提高升壓轉換器的效能,在開關週期的電流相位中開啟。圖7表示同步DC-DC升壓轉換器的拓撲,其應用印刷電路板(PCB)架構中,采用整合恩智浦(NXP)小訊號MOSFET的DC-DC降壓轉換器,因該MOSFET以SOT457、SOT23、SOT223和DFN2020MD-6(SOT1220)等小型表面組裝元件(SMD)技術封裝,將可提供極低的導通電阻及良好開關性能。

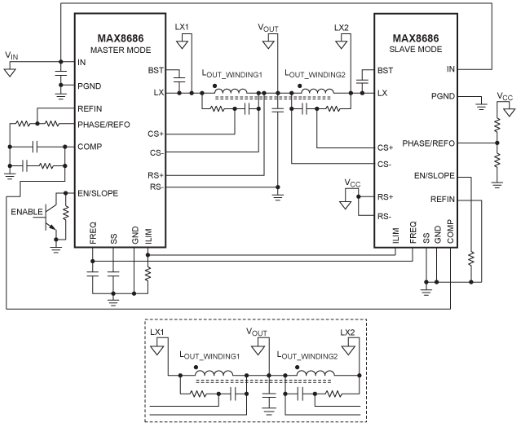

圖7 同步DC-DC降壓轉換器架構圖

該印刷電路板拓撲亦采用凌力爾特(Linear Technology)的控制器,以兩個N通道MOSFET構成開關層級,為讓高端開關能通過電感連接節(jié)點,直達輸入電源,必須進一步使用高于輸入電壓本身的控制電壓。

此一額外的電壓用于上級MOSFET的閘極控制,通過電荷幫浦產(chǎn)生,電容C25連接至開關節(jié)點、開關后的輸出,并通過蕭特基二極體連接穩(wěn)定電壓INTVCC(接腳12);INTVCC由內部5伏特低壓差線性穩(wěn)壓器(LDO)提供。

當?shù)投碎_關打開時,電容通過二極體充電,本例中,C25的一端接地,若Q2關閉、Q1打開,則充電后的電容連接至VIN,在接腳BOOST(接腳14)處,可測量電壓VIN+INTVCC–VF(二極體的正向電壓)。儘管此一升壓設計可正確驅動高端開關,但對于電荷幫浦而言,使用低電流蕭特基二極體便已足夠。

該設計采用的控制器還整合0.8伏特精密基準電壓源,用于輸出電壓調節(jié)。降壓轉換器的輸出返回至FB接腳。由R41+ R39和R38組成的電阻分壓器調節(jié)輸出電壓,可由公式12計算:

VOUT=0.8V×(1+(R41+R39)/R38)。。。(12)

假設控制器以恆定頻率工作,在高電流情況下可輕鬆控制DC-DC降壓轉換器的輸出電壓,但于低電流情況下對控制要求則升高,須大幅調整工作週期,或將控制器轉換為另一種控制模式,如高負載模式。該控制器有強制連續(xù)、高負載和脈衝跳躍叁種工作模式;其中,高負載模式具有高效率優(yōu)點,但漣波更大且電磁干擾(EMI)嚴重,最合適的模式須取決于終端應用的規(guī)格和需求。

可編程設計的開關頻率范圍為250k? 750kHz,頻率由電阻R30決定,控制器也可將內部振盪器與外部時鐘源同步(MODE/PLLIN,接腳1)。該模式下,RC網(wǎng)路須與接腳2(FREQ)相連,做為鎖相迴路(PLL)濾波器。

掌握電壓/電流漣波設計 中功率DC-DC轉換效率增

DC-DC轉換器有多種應用,具備外部MOSFET級的降壓轉換器控制器拓撲常用于運算和消費性電子產(chǎn)品中。新一代系統(tǒng)單晶片(SoC)解決方案須用到許多獨立的電源電壓,以提供主機板、筆記型電腦、平板裝置、電視或機上盒(STB)等裝置優(yōu)異的電源管理方案。

由于電源範圍最高可達數(shù)百瓦,最低僅數(shù)瓦,在桌上型電腦中,DC-DC轉換器須提供高達100安培的電流和130瓦功率,開關級MOSFET採用無損封裝(LFPAK)或QFN 5×6封裝的趨勢也逐漸盛行,一般筆電和小筆電的功率需求相對較小,功耗範圍為18~55瓦。開關MOSFET主要採用SO-8和QFN 3×3封裝。電視、機上盒或平板電腦等消費性電子的應用,功耗要求為7~15瓦。

對于中等功率範圍而言,目前可用QFN 3×3、QFN 2×2或SOT457等具有更小封裝的小訊號MOSFET來替代SO-8。為達到所需的電流漣波,須仔細選擇用于降壓轉換器的電感值。電流漣波更大,則輸出電壓漣波也更大;漣波增加,則電感更小、輸入電壓更高,若開關頻率降低,則將進一步增大。

ΔIL可由下列公式13算出:

ΔIL=VIN/L×ton=VOUT/L×toff.。。(13)

其中,T=ton+toff=1/f

得到公式14:

ΔIL=(VOUT/L)×(1–VOUT/VIN)×1/f.。。(14)

此時表示L=(VOUT/ΔIL)×(1–VOUT/VIN)×1/f。在極端情況下,電路會以連續(xù)模式的極限運行,電流在再次增大之前會完全降為零,可得出公式15: ΔIL=2×I(均值)。。。。。。(15)

代換ΔIL后,L=VOUT×(1–VOUT/VIN)/2×I(均值)×f

實際上,漣波電流ΔIL一般約為最大電流的30%,輸出電壓的漣波不僅取決于電感和ΔIL,還與輸出電容的電容值有關,電容愈大,漣波愈小。圖8為流入電容的電流波形圖,無損耗電容的計算方式如公式16:

圖8 電容電流與時間的關係示意圖

。。。。。。(16)

對于t0至t1,IC=ΔIL/ton×t;對于t1至t2,IC=ΔIL/toff×t。

電容漣波電壓如公式17所示:

。。。。。。(17)

當T=ton+toff=1/f時,可進一步得出公式18:

VC_ripple=ΔIL/(C×8×f)。。。。。。(18)

此外,實際電容須考慮等效串聯(lián)電阻(ESR),因此可得出公式19:

VC_ripple=ΔIL×(ESR+1(8×F×Cout))?(19)

做為開關的MOSFET則須考慮兩個損耗過程,一個是歐姆損耗,由剩余導通電阻RDSon造成;第二個損耗產(chǎn)生于開關瞬變。由于MOSFET并非理想的電源開關,從關閉到開啟狀態(tài)(或開啟到關閉)仍存有短暫的導通時間。

RDSon損耗也稱I2R損耗,可通過公式20計算(lout表示RMS值):

![]()

。。。。。。(20)

其工作週期為D=ton/T,項數(shù)1+δ包含與MOSFET的RDSon有關的溫度。δ典型值為δ=(0.005/℃)×(Tj–25℃)

低端開關則與其相似,由于當高端開關關閉時,同步MOSFET接通,因此I2R損耗可由公式21計算:

![]()

。。。。。。(21)

汲極電流/電壓影響MOSFET開關性能

至于轉變損耗,僅高端開關受此機制影響,塬因在于所採用的續(xù)流二極體(圖8中的D1)已接通,它將同步MOSFET上的電壓降至較小的正向電壓VF,若電路不含續(xù)流二極體,則情形有所不同。MOSFET的RDSon損耗須計入本體二極體的損耗,若不使用續(xù)流蕭特基二極體,則效率通常受較高的VF和本體二極體反向恢復時間的影響。

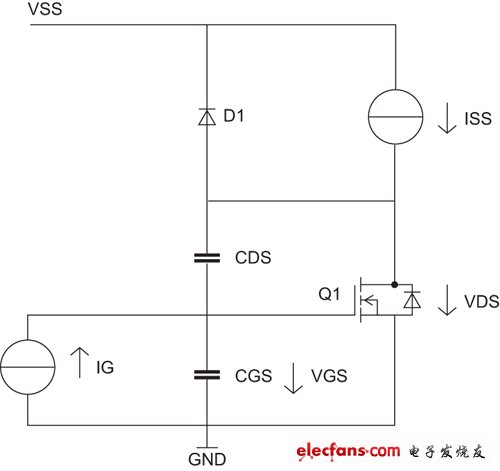

圖9表示MOSFET開關性能的測試電路,包含閘極至源極CGS、汲極至閘極CDG的寄生電容。電流源IG為控制閘極,在源極另一個電流源與一個續(xù)流二極體并聯(lián),隨后連接VSS,只要MOSFET為關閉狀態(tài),電流便流經(jīng)該二極體。導通過程中,若電流源IG打開,CGS的電壓線性上升,直至達到閘極-源極閾值電壓VGS(th)。此時開始有汲極電流通過,表示MOSFET在t0階段依然處于關閉狀態(tài)。

圖9 MOSFET開關性能測試塬理圖

汲極電流在t1階段上升。同時閘極電壓上升,直至達到VGS(pl)。VGS(pl)通常稱為MOSFET的臺階電壓。它在資料手冊中一般不會明確提及,但可由塬理圖中的閘極電荷與閘極-源極電壓衍生出來,在詳細資料手冊中可找到。t0和t1階段過后,電荷為Q0=Vpl×(CGS+CDS)。

在下一個t2階段,汲極電壓下降,閘極-源極電壓VGS保持恆定,為VGS(pl)。電荷Q1以相反方向對CDS充電,Q1=VSS ×CDS。CDS有別于雙極電晶體,它與米勒電容類似,且對MOSFET的開關性能有巨大影響。在t3階段閘極電壓再次增大,直到達到所需的最大閘極電壓,此時電流源被截流。FET的RDSon進一步降低。閘極驅動器提供額外的電荷Q2如公式22所示:

Q2=(VGS(t4)–VGS(pl))×(CGS+CDS)。。。(22)

總電荷則為QG=Q0+Q1+Q2,對功率MOSFET而言,該電荷可輕易超過100nC,計算方式如公式23:

IG=QG/ts.。。。。。(23)

由此可見,閘極電流可經(jīng)計算達到開關時間ts,若須較短的轉換時間,就要使用強大的驅動器控制MOSFET,以保持較低的開關損耗。在t1階段,MOSFET具有完全的輸入電壓,此時汲極電流增加;在下一個t2階段,ID定而汲極-源極電壓VDS下降,主要開關損耗均產(chǎn)生于這兩個開關階段;而t3階段損耗極小,可忽略,RDSon下降到最小值,此時達到最終VGS電壓。

開啟時的開關損耗發(fā)生于t1和t2階段,最主要損耗發(fā)生在t2,此時MOSFET的閘極電壓保持在臺階電壓V(pl)。損耗可由公式24計算:

PSW(on)=VIN×I/2×(t3+t1)×1/T?(24)

轉換器的開關頻率為fSW=1/T,MOSFET的關斷特性與開啟時類似。總開關損耗可由公式25計算:

PSW=VIN×1/T×(Imin/2×ton+Imax/ 2×toff)。。。。。。(25)

開關時間將取決于驅動器的電流驅動能力和MOSFET的閘極電阻,假設開啟和關斷時的驅動電流相等,則開關時間為tSW=QG/Idrive

LTC3851 tSW可由公式26估算:

tSW=QG×Rdrive/(Vdrive–VGS(th))。。。(26)

控制器的Rdrive約為2歐姆,與其有關的電壓是驅動器電壓INTVCC–V(th)。

小訊號MOSFET轉換/散熱效率俱優(yōu)

顯而易見,小訊號MOSFET適合中等功率DC-DC轉換,若閘極-源極電壓為4.5伏特,可提供15毫歐姆的RDSon,對SOT457元件而言,這是非常小的電阻,可提供更優(yōu)異的電源轉換效率,再加上採用銅片引線框架,讓封裝尺寸縮小,亦可具有良好散熱性能。

圖10是一張熱成像照片,說明此一參考設計的DC-DC轉換器PCB的輸出電流為6安培,并將電壓從10伏特降為1.5伏特,由于工作週期低至0.15,低端開關比高端開關散發(fā)更大的熱量;而該元件的溫度約為80℃,可推斷結點溫度Tj通常比封裝表面高5?10℃,故本測試中,Tj低于90℃。

圖10 內建DC-DC轉換器的PCB熱成像照片

高效率中等功率DC-DC轉換器可採用小訊號MOSFET設計,P通道MOSFET作為高端開關,與蕭特基二極體共同組成簡單轉換器,其中,蕭特基二極體須具低正向電壓,採用緊湊型扁平功率封裝,若還須進一步提升效率,則要改採同步DC-DC轉換器。

電子發(fā)燒友App

電子發(fā)燒友App

評論