3 設計實現

3.1 硬件設計

3.1.1 硬件架構

本文通過Zynq完成圖形生成與顯示功能,原理框圖如圖3所示,硬件模塊主要包括Zynq、DDR3SDRAM、FLASH、雙口RAM 等.正常工作時PS中的ARM 內核根據從雙口RAM 中接收到的繪圖指令和參數完成繪圖算法,將圖形數據寫入DDR3SDRAM 存儲器中.PL 從DDR3中讀出圖形數據進行顯示,并對DDR3SDRAM中的圖形數據進行清屏處理。

圖3 Zynq圖形生成原理框圖

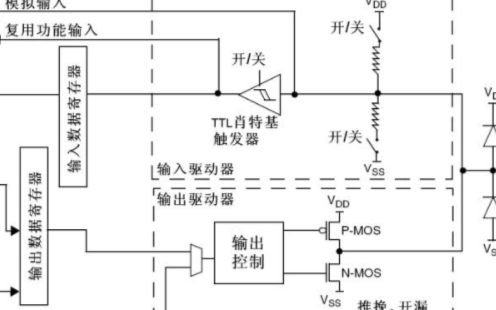

3.1.2 Zynq硬件平臺設計

本文通過Xilinx 的ISE14.2 軟件集成的XPS開發環境完成Zynq圖形生成電路的硬件平臺設計.利用XPS可以快速地對Zynq系統內的各種硬件資源進行定制設計,包括存儲器、外設、ARM 處理器、系統IP和用戶IP等.Zynq硬件平臺結構圖見圖4所示.

圖4 Zynq硬件結構圖

本文在Zynq中的PL 部分應用了VDMA、AXI2XSVI、XSVI2AXI、VTC等幾個IP核,其中VDMA 用于從DDR3SDRAM 中讀出圖形數據,同時向DDR3SDRAM 中寫入全零數據以達到清屏目的.AXI2XSVI用于將AXIGStream 數據流用行、場同步信號進行區隔,供外部顯示模塊進行顯示.XSVI2AXI用于將帶有行場同步信號的視頻數據轉換成AXIGStream 數據流.VTC 用于生成系統運行所需時序信號.對VTC根據顯示時序進行修改,系統即可產生多種分辨率圖形畫面。

3.1.3 圖形緩沖設計

本文中對DDR3SDRAM 幀存的操作包括3種類型:PS寫入、PL讀取、PL清零.清零從本質上說也是一種寫入操作,寫入的是全零數據.讀取和寫入請求通過DDR 控制器中的調度機制和仲裁策略分別在不同時刻得以響應,得益于DDR3SDRAM 的高速高帶寬優勢,外部可以同時進行多個通道的讀寫操作.針對本文中DDR3SDRAM 的3種操作類型,在DDR3幀存中設置了3個緩沖區,分別為buffer0,buffer1,buffer2,相應地,VDMA 中的framebuffer數目也設置為3.buffer的切換機制如表1所示.

這種三緩沖切換機制保證了寫入的都是已清零完成的buffer,清零的都是已讀出完成的buffer,讀出的都是已寫入完成的buffer。

根據buffer切換機制,VDMA 中的S2MM和MM2S通道分別以指定的buffer為操作對象.初始化狀態下為每個buffer指定默認的操作模式,而后在每個幀周期內啟動VDMA 切換buffer操作模式,從而不間斷地輸出圖形數據。

3.2 軟件設計

3.2.1 Zynq系統軟件

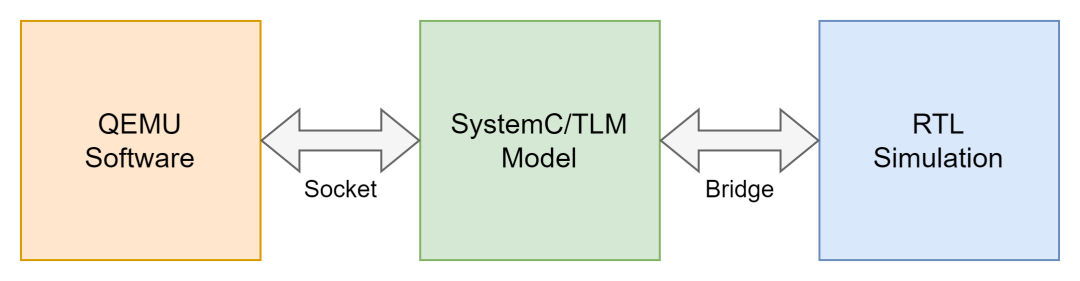

系統繪圖時,根據雙口RAM 提供的畫面內容要求,啟動繪圖任務,并將繪圖結果保存下來.顯示工作完全由PL內部的顯示邏輯負責,顯示邏輯從顯存中讀取顯示數據,按照標準時序送至顯示接口.圖形軟件的接口關系如圖5所示.

圖5 圖形生成軟件接口示意圖

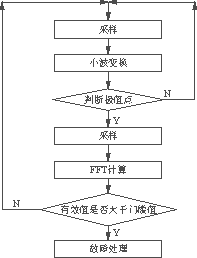

3.2.2 畫面顯示軟件

畫面顯示軟件主要包括初始化模塊和主模塊,結構如圖6所示.初始化模塊完成ARM 內核啟動;外設初始化信息加載;DDR3SDRAM、UART等設備初始化;VDMA 寄存器配置等初始化工作.運算控制模塊由雙口RAM 讀寫模塊;PS、PL 通信模塊以及繪圖模塊3部分組成,其中雙口RAM 讀寫模塊主要負責從雙口RAM中讀取繪圖指令數據,為繪圖模塊提供必要的繪圖參數;PS、PL通信模塊負責ARM 內核與VDMA的通信,切換緩存;繪圖模塊完成分配的繪圖任務,并將相應的計算結果,也即對應的像素點信息寫入DDR3SDRAM 中。

圖6 圖形生成軟件結構圖

電子發燒友App

電子發燒友App

評論