針對(duì)數(shù)字系統(tǒng)的設(shè)計(jì),我們經(jīng)常會(huì)遇到復(fù)位電路的設(shè)計(jì),對(duì)初學(xué)者來(lái)說(shuō)不知道同步復(fù)位與異步復(fù)位的區(qū)別與聯(lián)系,今天我對(duì)這個(gè)問(wèn)題簡(jiǎn)要的闡述下。

? ? ? ? 同步復(fù)位與異步復(fù)位原理

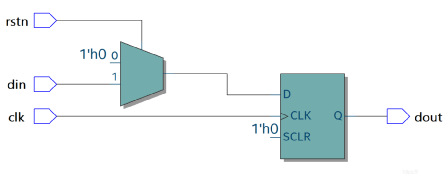

同步復(fù)位原理:同步復(fù)位只有在時(shí)鐘沿到來(lái)時(shí)復(fù)位信號(hào)才起作用,則復(fù)位信號(hào)持續(xù)的時(shí)間應(yīng)該超過(guò)一個(gè)時(shí)鐘周期才能保證系統(tǒng)復(fù)位。

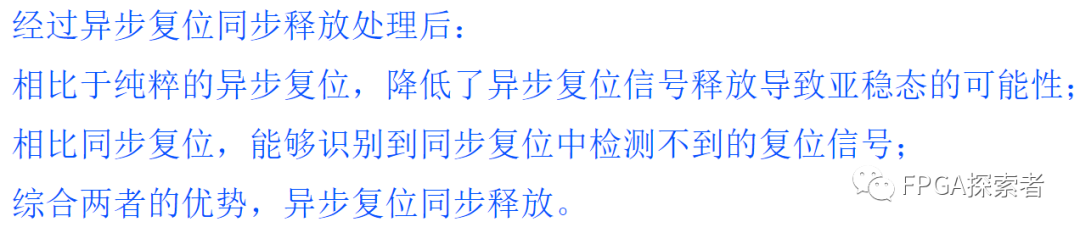

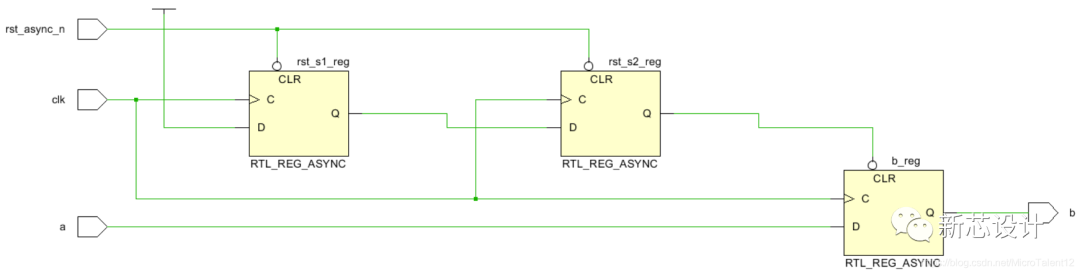

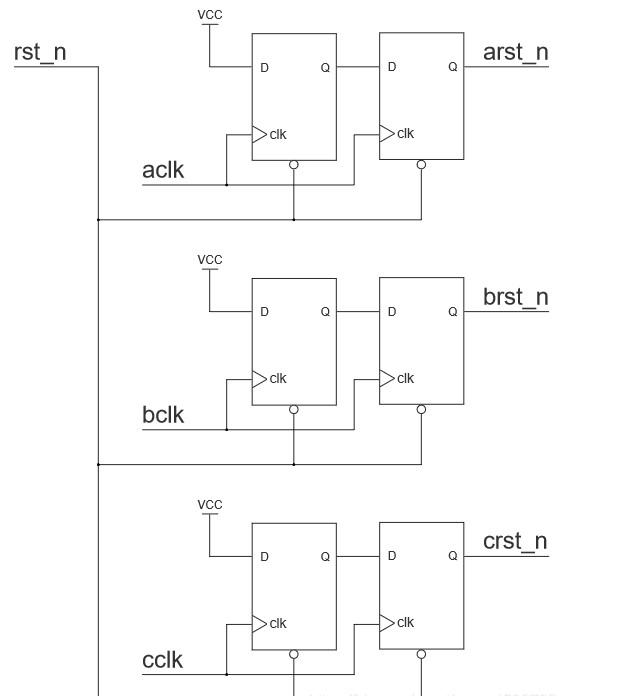

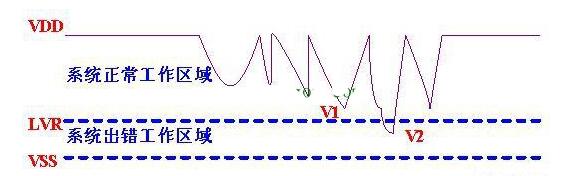

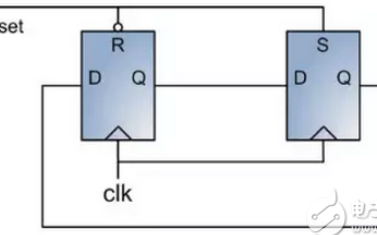

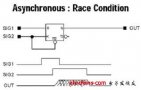

異步復(fù)位原理:異步復(fù)位只要有復(fù)位信號(hào)系統(tǒng)馬上復(fù)位,因此異步復(fù)位抗干擾能力差,有些噪聲也能使系統(tǒng)復(fù)位,因此有時(shí)候顯得不夠穩(wěn)定,要想設(shè)計(jì)一個(gè)好的復(fù)位最好使用異步復(fù)位同步釋放。

同步復(fù)位與異步復(fù)位的區(qū)別主要看是否有時(shí)鐘信號(hào)參與。異步復(fù)位不需要時(shí)鐘參與,一旦信號(hào)有效立即執(zhí)行復(fù)位操作;同步信號(hào)需要時(shí)鐘參與,只有有效的時(shí)鐘信號(hào)出現(xiàn),復(fù)位信號(hào)才有效。

一、同步復(fù)位與異步復(fù)位的特點(diǎn):

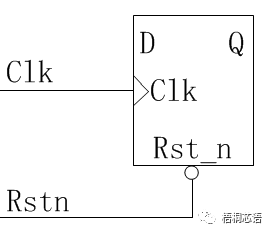

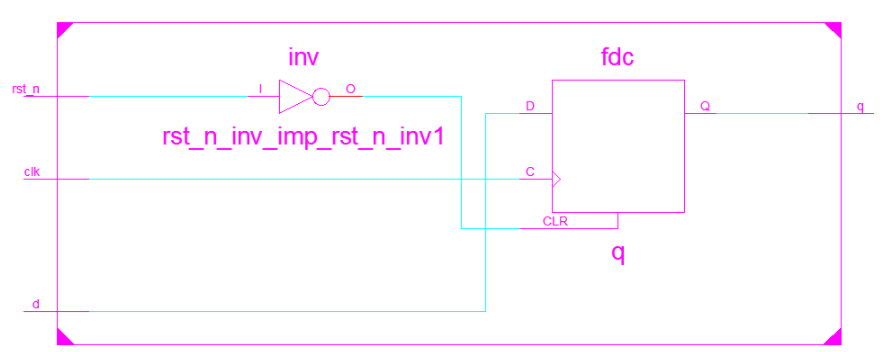

同步復(fù)位:顧名思義,同步復(fù)位就是指復(fù)位信號(hào)只有在時(shí)鐘上升沿到來(lái)時(shí),才能有效。否則,無(wú)法完成對(duì)系統(tǒng)的復(fù)位工作。用Verilog描述如下:

always @ (posedge clk) begin

if (!Rst_n)

。。。

end

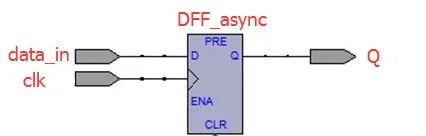

異步復(fù)位:它是指無(wú)論時(shí)鐘沿是否到來(lái),只要復(fù)位信號(hào)有效,就對(duì)系統(tǒng)進(jìn)行復(fù)位。用Verilog描述如下:

always @ (posedge clk or negedge Rst_n) begin

if (!Rst_n)

?

。。。

end

二、同步復(fù)位和異步復(fù)位的優(yōu)缺點(diǎn)分析:

1、總的來(lái)說(shuō),同步復(fù)位的優(yōu)點(diǎn)大概有3條:

b、可以使所設(shè)計(jì)的系統(tǒng)成為100%的同步時(shí)序電路,這便大大有利于時(shí)序分析,而且綜合出來(lái)的fmax一般較高。

c、因?yàn)樗挥性跁r(shí)鐘有效電平到來(lái)時(shí)才有效,所以可以濾除高于時(shí)鐘頻率的毛刺。他的缺點(diǎn)也有不少,主要有以下幾條:

a、復(fù)位信號(hào)的有效時(shí)長(zhǎng)必須大于時(shí)鐘周期,才能真正被系統(tǒng)識(shí)別并完成復(fù)位任務(wù)。同時(shí)還要考慮,諸如:clk skew,組合邏輯路徑延時(shí),復(fù)位延時(shí)等因素。

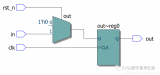

b、由于大多數(shù)的邏輯器件的目標(biāo)庫(kù)內(nèi)的DFF都只有異步復(fù)位端口,所以,倘若采用同步復(fù)位的話,綜合器就會(huì)在寄存器的數(shù)據(jù)輸入端口插入組合邏輯,這樣就會(huì)耗費(fèi)較多的邏輯資源。

2、對(duì)于異步復(fù)位來(lái)說(shuō),他的優(yōu)點(diǎn)也有三條,都是相對(duì)應(yīng)的

a、大多數(shù)目標(biāo)器件庫(kù)的dff都有異步復(fù)位端口,因此采用異步復(fù)位可以節(jié)省資源。

b、設(shè)計(jì)相對(duì)簡(jiǎn)單。

c、異步復(fù)位信號(hào)識(shí)別方便,而且可以很方便的使用FPGA的全局復(fù)位端口GSR。

缺點(diǎn):

a、在復(fù)位信號(hào)釋放(release)的時(shí)候容易出現(xiàn)問(wèn)題。具體就是說(shuō):倘若復(fù)位釋放時(shí)恰恰在時(shí)鐘有效沿附近,就很容易使寄存器輸出出現(xiàn)亞穩(wěn)態(tài),從而導(dǎo)致亞穩(wěn)態(tài)。

b、復(fù)位信號(hào)容易受到毛刺的影響。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論