異步復位的verilog程序如下:

moduleD_FF

(

//Inputports

SYSCLK

,RST_B,

A,

//Outputports

B

);

//=========================================

//Inputandoutputdeclaration

//=========================================

inputSYSCLK;

input RST_B;

inputA;

outputB;

//=========================================

//Wireandregdeclaration

//=========================================

wireSYSCLK;

wireRST_B;

wireA;

regB;

//=========================================

//Logic

//=========================================

always@(posedgeSYSCLKornegedgeRST_B)

begin

if(!RST_B)

B《=1‘b0;

else

B《=A;

end

endmodule

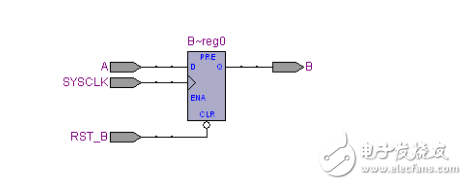

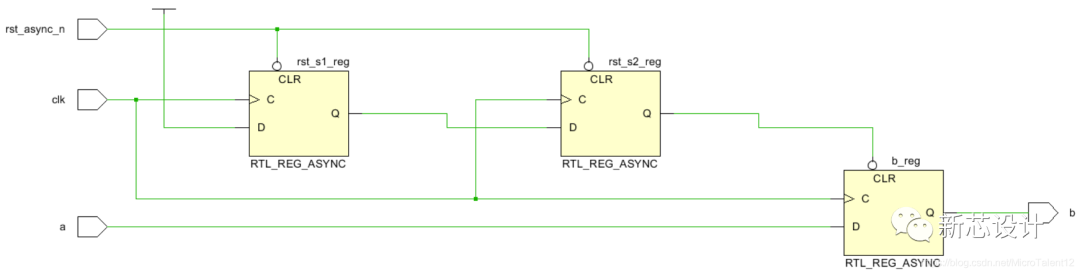

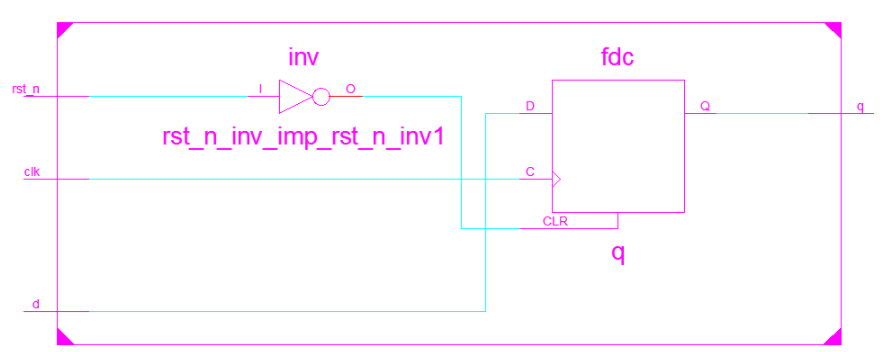

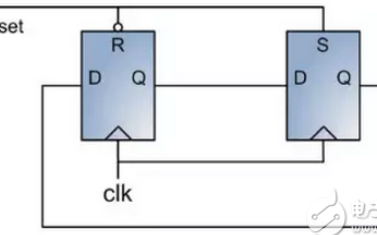

綜合后的RTL級電路圖如下:

通過比較顯然異步復位消耗的邏輯資源要少些,因此通常的設計中都采用異步復位的方式,需要進一步的學習的話,可以再研究下其它的資料。

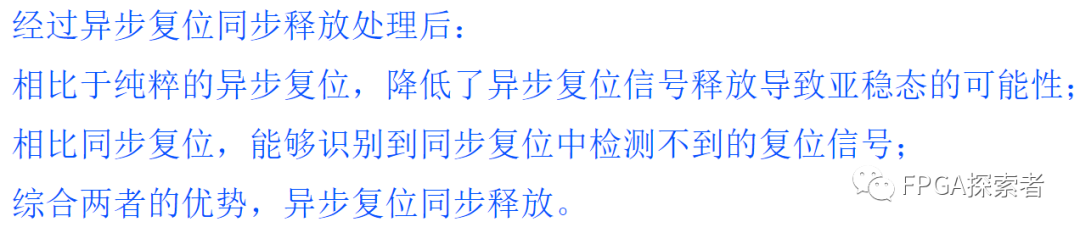

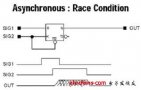

三、總結:

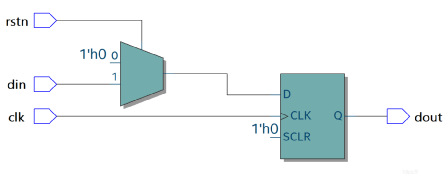

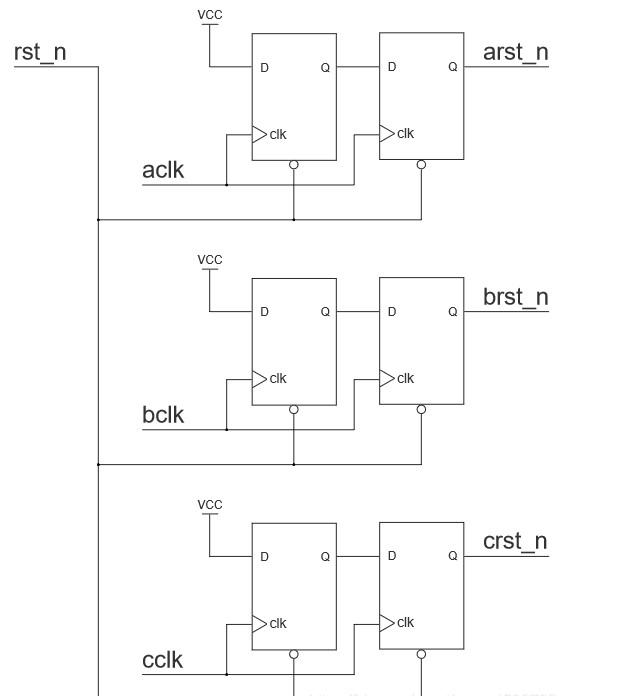

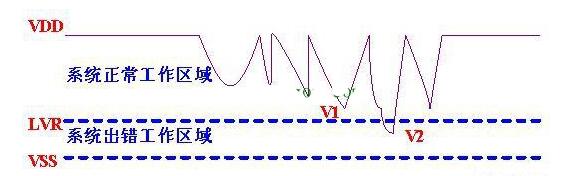

所以說,一般都推薦使用異步復位,同步釋放的方式,而且復位信號低電平有效。這樣就可以兩全其美了。

電子發燒友App

電子發燒友App

評論