您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 嵌入式技術(shù) > FPGA/ASIC技術(shù) >

龍芯處理器IP核的FPGA驗(yàn)證平臺(tái)設(shè)計(jì)(3)

2012年04月21日 15:22 來源:本站整理 作者:秩名 我要評(píng)論(0)

將已經(jīng)成熟的AMBA總線IP核的Verilog代碼通過Synplify綜合,利用Altera公司的QUARTUS Ⅱ軟件作布局布線,燒人Cyclone Ⅱ EP2C70,再用同樣的方式將新開發(fā)的EMI IP核的Verilog代碼燒入該FPGA,將其中的SDRAM控制器作為驗(yàn)證示例,選取其中最簡(jiǎn)單的訪問方式來驗(yàn)證該平臺(tái)能否使用。上電后,首先要對(duì)所有內(nèi)存區(qū)(bank)預(yù)充電,經(jīng)8個(gè)自刷新周期后需要設(shè)置訪問模式,即編程模式寄存器。以上三個(gè)過程要求如下:

(1)預(yù)充電命令的發(fā)出要求:在時(shí)鐘周期的上升沿處,CS、RAS、WE為低,CAS為高。

(2)自刷新命令的發(fā)出要求:在時(shí)鐘周期的上升沿處,CS、RAS、CAS 禾口CKE保持低,WE為高。

(3)模式寄存器的激活:在時(shí)鐘的上升沿處,RAS、CAS、CS和WE為低。

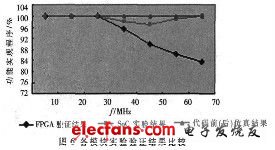

當(dāng)要驗(yàn)證各個(gè)IP模塊(包括[NT中斷控制器、DMA控制器、LCD控制器和AC97控制器等)之間的協(xié)同工作時(shí),燒入的代碼較多,占用的FPGA資源也較多,再加上需要實(shí)時(shí)運(yùn)行,例如播放PM3實(shí)時(shí)解碼過程中,時(shí)鐘至少要求60 MHz,需要工作的IP核有總線、DMA控制器、INT中斷控制器、AC97控制器等,因此在這種情況下,最好使用Multi PointSynthesis的綜合流程和Timing driv-en的綜合與優(yōu)化策略,并使用Logic一lock約束技術(shù)和人工干預(yù)布局布線,以達(dá)到預(yù)期目的。使用該平臺(tái)對(duì)所開發(fā)的SoC的各個(gè)模塊進(jìn)行了驗(yàn)證,并在lO MHz~70 MHz條件下與代碼前(后)仿真結(jié)果和SoC實(shí)測(cè)結(jié)果進(jìn)行了比較,發(fā)現(xiàn)該FPGA驗(yàn)證平臺(tái)在多模塊、高速情況下,性能有所下降,如圖6所示,需進(jìn)一步提高綜合和布局布線技術(shù)。

圖6各模塊實(shí)驗(yàn)驗(yàn)證結(jié)果比較

本文設(shè)計(jì)了基于國(guó)產(chǎn)龍芯I號(hào)處理器IP核的SoC的FPGA驗(yàn)證平臺(tái),介紹了怎樣利用該平臺(tái)進(jìn)行軟硬件協(xié)同設(shè)計(jì)、SoC系統(tǒng)移植、IP核驗(yàn)證和運(yùn)行實(shí)時(shí)操作系統(tǒng)。在電壓設(shè)計(jì)、模塊選用甚至處理器核的選用方面都考慮了升級(jí)擴(kuò)展技術(shù),可為其他SoC的驗(yàn)證所借鑒。驗(yàn)證結(jié)果表明,基于龍芯I號(hào)CPU IP核的SoC可成功運(yùn)行Linux嵌入式程序及VxWorks。

本文導(dǎo)航

- 第 1 頁(yè):龍芯處理器IP核的FPGA驗(yàn)證平臺(tái)設(shè)計(jì)(1)

- 第 2 頁(yè): FPGA的典型開發(fā)流程

- 第 3 頁(yè):驗(yàn)證平臺(tái)的檢驗(yàn)

用戶評(píng)論

發(fā)表評(píng)論

龍芯處理器業(yè)界動(dòng)態(tài)

龍芯處理器技術(shù)應(yīng)用

IP核技術(shù)應(yīng)用

IP核資料下載

- 基于FPGA的DDS IP核設(shè)計(jì)方案

- 基于SOPC技術(shù)的異步串行通信IP核的設(shè)計(jì)

- RapidIO應(yīng)用系統(tǒng)及其驗(yàn)證模型的設(shè)計(jì)與測(cè)試

- 基于NiosII步進(jìn)電機(jī)控制器IP核的設(shè)計(jì)與實(shí)現(xiàn)

- JPEG解碼器IP核設(shè)計(jì)

- Wishbone總線實(shí)現(xiàn)UART IP核設(shè)計(jì)

- 基于層次模型的USB2.0接口芯片IP核固件的設(shè)計(jì)

- USB2.0接口芯片IP核固件設(shè)計(jì)

- AMBA總線IP核的設(shè)計(jì)

- AMBA2.0總線IP核的設(shè)計(jì)與實(shí)現(xiàn)