局部子系統可以通過軟件控制復位狀態,一共有六個RM__RSTCTRL寄存器分別控制Always On之外的六個電源域下的局部子系統的復位:

● RM_ACTIVE_RSTCTRL控制DSP的復位;

●RM_DEFAULT_RSTCTRL控制PCIe,MMU和兩個M3的復位。

● RM_SGX_RSTCTRL控制SGX的復位。

● RM_IVAHD0_RSTCTRL,RM_IVAHD1_RSTCTRL,RM_IVAHD2_RSTCTRL控制視頻協處理的復位。

2.3 時鐘管理

時鐘經FAPLL(Flying Adder PLL)倍頻后輸入PRCM,PRCM對時鐘的控制管理分為三個方面:

● 模塊時鐘頻率的配置由CM__CLKSEL[CLKSEL]控制;

●時鐘域的開關由CM___CLKSTCTRL控制;

● 模塊時鐘開關由CM___CLKCTRL控制;

由上可以看出系統架構的劃分,首先是按電源域,然后按時鐘域,最后才是對模塊獨立的時鐘控制。為達到省電的目的,在不能對整個電源域關閉的情況下,要看時鐘域是否有模塊被使用,如果沒有,則可將時鐘域關閉,否則,就只能將相應的模塊時鐘關閉。

以系統中用到EMIF0,但不用EMIF1為例說明如何配置PRCM控制電源域,時鐘域,以及模塊時鐘。

● EMIF屬于Default電源域,PM_DEFAULT_PWRSTCTRL寄存器只有一個控制位控制整個default電源域的開關,因為EMIF0要使能,所以這個寄存器必需使能,也就是不能關閉整個default電源域。

WR_MEM_32(PM_DEFAULT_PWRSTCTR, 0x2);

while((RD_MEM_32(PM_DEFAULT_PWRSTCTR) & 0x3000)!=0x3000);

● 配置EMIF的時鐘域,EMIF時鐘屬于L3_FAST_DEFAULT_GCLK時鐘域,由寄存器CM_DEFAULT_L3_FAST_CLKSTCTRL 控制,DMM,EMIF_FW也屬于這個時鐘域,所以這個時鐘域需要使能。

WR_MEM_32(CM_DEFAULT_L3_FAST_CLKSTCTRL, 0x2);

while((RD_MEM_32(CM_DEFAULT_L3_FAST_CLKSTCTRL) & 0x300)!=0x300);

● 配置EMIF模塊時鐘,EMIF0,EMIF1的模塊時鐘分別由CM_DEFAULT_EMIF_0_CLKCTRL和CM_DEFAULT_EMIF_1_CLKCTRL單獨控制。

WR_MEM_32(CM_DEFAULT_EMIF_0_CLKCTRL, 0x2); // Enable EMIF0 Clock

while(RD_MEM_32(CM_DEFAULT_EMIF_0_CLKCTRL)!=0x2);

WR_MEM_32(CM_DEFAULT_EMIF_1_CLKCTRL, 0x0); // Disable EMIF1 Clock

while((RD_MEM_32(CM_DEFAULT_EMIF_1_CLKCTRL) & 0x3000)!=0x3000);

3.DSP MMU配置

DM816x DSP上首次使用了MMU,MMU(Memory Management Unit)的作用是:

● 提供硬件機制的虛擬地址與物理地址轉換;

● 提供硬件機制的內存訪問權限授權。

對于支持多進程的HLOS(High Level Operation System),OS利用MMU的地址轉換功能可以為每個進程提供獨立的地址空間。但對于DSP來說,通常不運行HLOS, 這種功能得不到體現。

在ARM+DSP的雙核SOC架構上,所有外設包括內存空間都是共享的,平等訪問,這樣的架構有很多好處,比如在兩個核間共享數據很高效,只需要傳遞數據的指針,不需要做數據的拷貝;但是帶來的問題是需要用戶程序保證不會非法改寫另一個核的程序數據空間,否則會導致系統崩潰,而且這種問題導致的現象不確定,通常難以精確定位。

ARM上的HLOS如Linux的內存管理,可以保證不會非法訪問系統管理之外的空間。在以往的DaVinci系列芯片上DSP沒有MMU,需要用戶保證DSP程序不會非法訪問ARM的程序和數據空間。DM8168的DSP上使用MMU以硬件方式提供了內存訪問授權,使內存訪問越界問題的定位變得格外容易, MMU的錯誤狀態寄存器會記錄越界訪問,并且MMU_FAULT_AD會記錄最近通過MMU的訪問地址。

MMU可以工作在旁通模式,即不對地址做映射,但是在DM816x上GPMC的系統地址空間于0x0地址開始,與DSP的片內地址空間重疊,如果DSP需要訪問GPMC,必需要通過MMU將GPMC的空間映射到虛擬空間。

MMU的TLB(Translation Look-aside Buffer)配置分為兩種:TWL(Table Walking Logic)模式,和靜態TLB模式;TWL模式功能靈活,靜態TLB模式轉換效率高[5].

通常DSP上不運行HLOS,建議采用靜態TLB模式。一張超級映射表可以映射16MByte空間,TLB共可容納32張表,最多可以映射512MByte空間。由于外設通常由ARM控制,DSP訪問部分GPMC和部分DDR空間,以及部分外設,所以512MByte空間能滿足絕大多數應用的DSP訪問空間需求。目前UBoot中沒有DSP MMU的配置,用戶在DSP訪問片外空間之前完成MMU的配置即可。

4 DDR配置

DM816x的DDR控制器兼容支持DDR2和DDR3;有兩個獨立的控制器,各有兩個片選;每個DDR控制器的地址空間為1GByte;與TI以往處理器不同的是在DM816x上片選與地址空間的映射是可配置的,每個片選上的地址空間大小也是可配置的。所以在DM816x上的DDR配置分為三部分:

●DDR時鐘配置

●DDR地址空間映射,

●DDR時序配置

4.1 DDR時鐘配置

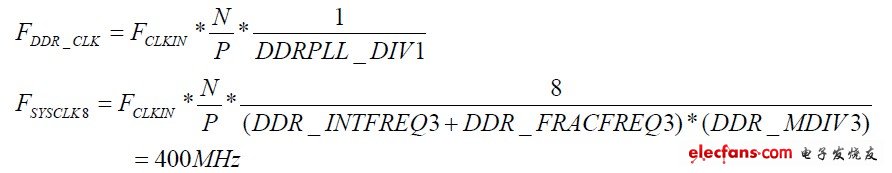

DDR時鐘FAPLL配置計算方法參見前面時鐘配置部分。DDR時鐘包括兩部分:接口時鐘,模塊功能時鐘。

接口時鐘即FDDR_CLK由DDR FAPLL的Fvco經DDRPLL_DIV1分頻輸出。

DDR模塊功能時鐘FSYSCLK8固定為400MHz以與內部總線L3時鐘同步, 無論DDR接口時鐘多少,都將SYSCLK8配置為400MHz.

DDR時鐘計算公式:

?

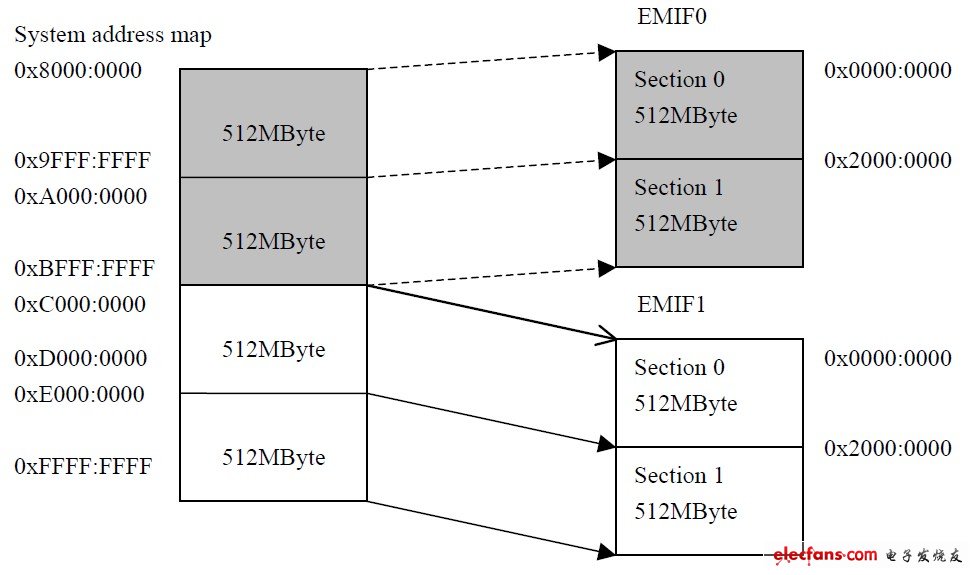

4.2 DDR地址空間映射

DDR空間尋址范圍共2GB,最多可分為4段,通過DMM的DMM_LISA_MAP0~3分別配置EMIF0的CS0,CS1和EMIF1的CS0和CS1的首地址映射,及兩個DDR控制器之間的尋址方式。兩個DDR控制器之間的尋址方式有兩種模式:非交織訪問,交織訪問。

非交織訪問,即兩個控制器的尋址在各自的映射范圍內線性遞增。如果希望將ARM與DSP的內存空間在物理上分開,可以選擇這種模式。當只使用一個控制器時,只能使用非交織的線性尋址模式。

交織訪問,即雙通道內存技術,當訪問在控制器A上進行時,控制器B為下一次訪問做準備,數據訪問在兩個控制器上交替進行,從而提高DDR吞吐率。支持128byte,256byte,512byte的交織模式。如果要使用交織模式,要保證兩個控制器上有對稱的物理內存:即兩塊內存大小一致;在各自的控制器上的地址映射一致。

以兩個控制器上的CS0,CS1各接512MByte內存,共2GByte內存為例,非交織線性訪問模式的配置為:

/*Program the DMM to Access EMIF0*/

WR_MEM_32(DMM_LISA_MAP__0, 0x80500100);

WR_MEM_32(DMM_LISA_MAP__1, 0xA0500120);

/*Program the DMM to Access EMIF1*/

WR_MEM_32(DMM_LISA_MAP__2, 0xC0500200);

WR_MEM_32(DMM_LISA_MAP__3, 0xE0500220);

示意圖見4.1.

?

圖4.1 線性訪問模式

電子發燒友App

電子發燒友App

評論