介紹了一種應(yīng)用于通用微處理器系統(tǒng)中的SDRAM與雙口RAM之間的數(shù)據(jù)轉(zhuǎn)移接口控制電路,由VHDL語言設(shè)計,用Xilinx公司4000系列FPGA實現(xiàn),目前該電路硬件實現(xiàn)和微處理器系統(tǒng)已經(jīng)通過驗證,證

2011-11-11 09:43:14 1415

1415

為了在嵌入式系統(tǒng)設(shè)計中實現(xiàn)對SDRAM存儲器的訪問,本文提出了一種基于AMBA-AHB總線規(guī)范的SDRAM控制器設(shè)計方案。方案首先簡要介紹了AMBA總線規(guī)范,然后在完成整個存儲控制器的整體框架

2014-01-02 13:59:42 4102

4102

在高速實時或者非實時信號處理系統(tǒng)當中,使用大容量存儲器實現(xiàn)數(shù)據(jù)緩存是一個必不可少的環(huán)節(jié),也是系統(tǒng)實現(xiàn)中的重點和難點之一。SDRAM(同步動態(tài)隨機訪問存儲器)具有價格低廉、密度高、數(shù)據(jù)讀寫速度快的優(yōu)點

2018-01-18 07:21:00 7964

7964

基于SDRAM控制器實現(xiàn)FPGA模塊化和通用性的解決方案設(shè)計

2020-12-22 07:58:55

上找到了幾個sdram控制器,但是我無法存儲或讀取任何內(nèi)容。我問的是你有沒有改變sdram的工作代碼并使它像sram那樣我可以測試我的硬件?你有什么想法我怎么測試芯片是否存活?最好的祝福。我喜歡

2019-05-16 13:10:57

SDRAM控制器用戶手冊主要內(nèi)容包括功能特點、整體框圖、工作原理、信號定義、參數(shù)介紹、GUI 調(diào)用、接口時序等。主要用于幫助用戶快速了解高云半導體 SDRAM 控制器的產(chǎn)品特性、特點及使用方法。

2022-10-08 07:48:27

和后仿真。以上介紹了一種應(yīng)用于通用微處理器系統(tǒng)中的SDRAM與雙口RAM之間的數(shù)據(jù)轉(zhuǎn)移接口控制電路,由VHDL語言設(shè)計,用Xilinx公司4000系列FPGA實現(xiàn),目前該電路硬件實現(xiàn)和微處理器系統(tǒng)已經(jīng)通過驗證,證明可將SDRAM作為高速、大容量存儲器應(yīng)用在簡單電子系統(tǒng)中。

2019-06-10 05:00:08

描述此參考設(shè)計演示了如何實現(xiàn) SDRAM 存儲器并通過接口連接到高性能微控制器 TM4C129XNCZAD。為了實現(xiàn)此設(shè)計,其中采用了該微控制器的 EPI 接口來連接 256Mbit SDRAM

2018-08-30 09:31:51

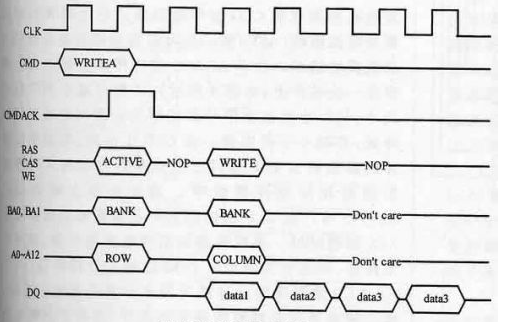

SDRAM的基本工作原理是什么SDRAM的基本讀寫操作步驟是什么一種簡單的通用SDRAM控制器的實現(xiàn)

2021-05-10 06:26:44

DDR SDRAM參考設(shè)計VHDL版(有詳細的文檔,仿真綜合文件)File/Directory Description

2012-08-11 09:33:30

DDR_SDRAM控制器的VHDL代碼已經(jīng)測試

2016-08-24 16:49:35

本次發(fā)布三例 SDRAM 控制器參考設(shè)計及 IP Core Generator 支持調(diào)用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

USB接口控制器參考設(shè)計,xilinx提供VHDL代碼

2012-08-15 14:54:06

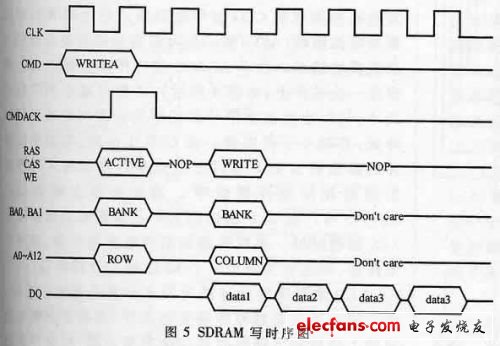

第六講已介紹完SDRAM的寫模塊,而在這一講中,我們會接著介紹SDRAM控制器的讀模塊。在搞定讀模塊之后,就相當于SDRAM控制器部分已經(jīng)搭建好了,想一想還是很期待的哦,哈哈,大家先別急。在這一講中

2017-05-08 22:28:13

使用Verilog實現(xiàn)基于FPGA的SDRAM控制器

2012-08-20 19:35:27

分享一款不錯的SDRAM接口的VHDL設(shè)計

2021-05-08 06:04:27

本文介紹一種通用SDRAM控制器的FPGA模塊化解決方案。

2021-05-07 06:42:49

控制器。為了使微控制器的數(shù)據(jù)總線(8位)與SDRAM控制器的數(shù)據(jù)總線(32位)相匹配,利用VHDL語言實現(xiàn)8位到32位的雙向數(shù)據(jù)轉(zhuǎn)換,使整個數(shù)據(jù)獲取系統(tǒng)能可靠正常工作。 3. VHDL程序設(shè)計

2016-05-08 06:18:34

應(yīng)用VHDL語言設(shè)計數(shù)字系統(tǒng),大部分設(shè)計工作可在計算機上完成,從而縮短系統(tǒng)開發(fā)時間,提高工作效率。下面介紹基于VHDL設(shè)計交通燈控制器的一種方案,并給出源程序和仿真結(jié)果。

2019-10-18 07:21:51

為降低設(shè)計成本,縮短設(shè)計周期,提出一種基于VHDL的洗衣機控制器的設(shè)計方案。

2019-09-30 07:43:39

。DDR的時序與SDRAM是相似的,學好SDRAM后,理解DDR2和DDR3就非常容易了。2、至簡設(shè)計代碼實現(xiàn)(附錄部分代碼)下面是使用至簡設(shè)計法實現(xiàn)的SDRAM控制器,該控制器使用了四段式狀態(tài)機,其他信號

2017-08-02 17:43:35

基于FPGA的SDRAM控制器設(shè)計(原創(chuàng)分享)—自動刷新設(shè)計作者:小周本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請注明出處!SDRAM控制器設(shè)計的主要功能是能對SDRAM進行讀寫操作,本工程實現(xiàn)了SDRAM

2020-04-15 14:43:50

本文提出了一種基于FPGA的SDRAM控制器的設(shè)計方法,并用Verilog給于實現(xiàn),仿真結(jié)果表明通過該方法設(shè)計實現(xiàn)的控制器可以在FPGA芯片內(nèi)組成如圖1所示的SDRAM接口,從而使得系統(tǒng)用戶對SDRAM的操作非常方便。

2021-04-15 06:46:56

基于FPGA的SDRAM控制器包括哪些部分呢?如何去實現(xiàn)一種基于FPGA的SDRAM控制器設(shè)計呢?

2021-11-04 06:47:44

SDRAM控制器基本操作原理是什么?如何去設(shè)計并實現(xiàn)一種SDRAM控制器?

2021-06-07 06:01:39

如何解決SDRAM控制器設(shè)計刷新的問題?

2021-11-04 07:20:02

本文介紹VHDL-AMS的新概念和新特性。通過對PID控制原理進行數(shù)學分析,建立PID控制器的數(shù)學模型,實現(xiàn)PID控制器的VHDL-AMS行為級建模,并進行仿真分析。

2021-05-06 07:59:57

本文介紹一種使用硬件描述語言VHDL來實現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對問題進行建模,并對模型進行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對Petri網(wǎng)

2019-08-16 07:52:03

通過對傳統(tǒng)MCS-51單片機指令時序和體系結(jié)構(gòu)的分析,使用VHDL語言采用自頂向下的設(shè)計方法重新設(shè)計了一個高效的微控制器內(nèi)核。

2021-04-13 06:10:59

最近想寫 SDRAM的讀寫。哪些命令看到 云里霧里的 ,有沒好人發(fā)給 調(diào)通的 VHDL 程序 ,給個參考學習下。拜謝了{:4:}{:4:}

2013-02-25 16:04:55

我移植網(wǎng)上的一個sdram vga的代碼到ep4ce6e22c8n開發(fā)板上,它里面的sdram控制器是tequan寫的,但是我移植后,卻得不到代碼要的效果,sdram讀寫出來的數(shù)據(jù)有錯,調(diào)了好久也

2014-04-03 16:23:55

DDR SDRAM在嵌入式系統(tǒng)中有哪些應(yīng)用?DDR SDRAM的工作方式有哪幾種?怎樣去設(shè)計DDR SDRAM控制器?

2021-04-30 07:04:04

SDRAM控制器的主要特點是什么?SDRAM控制器的狀態(tài)流程是怎樣的?SDRAM控制器有哪些功能?

2021-06-26 07:35:01

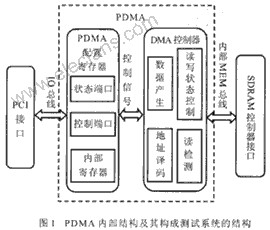

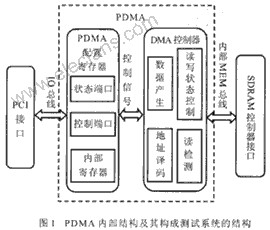

用什么方法去測試SDRAM控制器的性能?PDMA的結(jié)構(gòu)及工作原理是什么?RTL仿真的順序是什么?

2021-04-08 06:19:50

的內(nèi)存控制器的設(shè)計與應(yīng)用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存儲器接口設(shè)計.pdf一種采用FPGA設(shè)計的SDRAM控制器.pdf用Xilinx+FPGA實現(xiàn)DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

SDRAM(同步動態(tài)存儲器)是一種應(yīng)用廣泛的存儲器,具有容量大、數(shù)據(jù)讀寫速度快、價格低廉等優(yōu)點,特別適合那些需要海量存儲器的應(yīng)用領(lǐng)域,例如視頻方面。那么有誰知道,高速SDRAM控制器的視頻有哪些嗎?

2019-08-09 06:23:43

SDR SDRAM控制器1?標準SRD SDRAM控制器參考設(shè)計,altera提供 使用手冊 VHDL代碼 Verilog代碼?SDR SDRAM控制器2 標準SRD SDRAM控制器參考設(shè)計,xilinx提供 使用手冊 VHDL代碼Verilog

2008-05-20 10:58:59 155

155 介紹基于現(xiàn)場可編程門陣列(FPGA),利用VHDL 語言設(shè)計實現(xiàn)MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結(jié)構(gòu)、SDRAM 存儲接口結(jié)構(gòu)和SDRAM 控制狀態(tài)機的設(shè)計。

2009-05-15 14:47:29 24

24 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

51 ref-sdr-sdram-vhdl代碼

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:52:53 46

46

SDRAM控制器參考設(shè)計,Lattice提供的VHDL源代碼

-- Permission:

-- Lattice Semiconductor grants

2009-06-14 08:54:28 93

93 提出了一種在HDTV SOC 系統(tǒng)中實現(xiàn)多模塊共享存儲單元的高效SDRAM 控制器。通過利用合理的請求仲裁、Full Page 讀寫、指令與數(shù)據(jù)分離、指令緩存和前后相關(guān)處理等機制,實現(xiàn)了高吞吐

2009-08-14 16:09:14 13

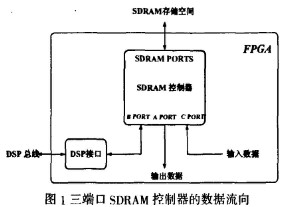

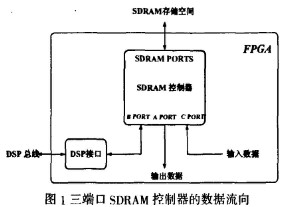

13 設(shè)計實現(xiàn)了一種基于FPGA 的,可用于多數(shù)據(jù)緩存的、能夠高效利用帶寬的多端口SDRAM 控制器。本文使用狀態(tài)機的設(shè)計思想,采用Verilog 硬件描述語言設(shè)計了時序控制程序。得到的SDR

2009-08-27 09:43:33 22

22 簡要介紹了SDRAM工作原理并認真研究了Altera提供的SDRAM控制器,根據(jù)實際系統(tǒng)使用需要加以修改簡化,設(shè)計了對修改后控制器進行操作的狀態(tài)機。采用全頁突發(fā)讀寫模式,每次讀/寫

2009-12-26 17:02:56 70

70 DDR2 SDRAM控制器的設(shè)計與實現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計方法!詳述了其基本結(jié)構(gòu)和設(shè)計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實現(xiàn)了一個三端口非透明型SDRAM 控制器,該控制器面向用戶具有多個端口,通過輪換優(yōu)先級的設(shè)計保證了多個端口平均分配SDRAM的帶寬且不會降

2010-03-03 14:37:14 11

11 簡要介紹了SDRAM工作原理并認真研究了Altera提供的SDRAM控制器,根據(jù)實際系統(tǒng)使用需要加以修改簡化,設(shè)計了對修改后控制器進行操作的狀態(tài)機。采用全頁突發(fā)讀寫模式,每次讀/寫后自動

2010-07-21 17:31:37 38

38 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計思想,分析了各模塊功能與設(shè)計注意事項,并

2010-07-30 17:13:55 30

30 介紹基于VHDL的微型打印機控制器的設(shè)計。論述了微型打印機的基本原理,以及實現(xiàn)控制器的VHDL語言設(shè)計。打印機的數(shù)據(jù)來自系統(tǒng)中的存儲模塊,根據(jù)需要控制打印。該微型打印機控

2010-12-23 16:44:19 60

60 摘要: 介紹了SDRAM的存儲體結(jié)構(gòu)、主要控制時序和基本操作命令,并且結(jié)合實際系統(tǒng),給出了一種用FPGA實現(xiàn)的通用SDRAM控制器的方案。

關(guān)鍵詞:

2009-06-20 12:51:58 834

834

摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設(shè)計方法,使用該方法實現(xiàn)的控制器可非常方便地對SDRAM進行控制。

關(guān)鍵

2009-06-20 13:04:51 2075

2075 我們設(shè)計了一個PDMA(Programmable Direct Mem o ry Access)用于測試SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多個IP模塊(圖形處理單元,音頻處理單元等)交換數(shù)據(jù),采用多個PDMA通道

2010-07-02 18:31:41 1655

1655

SDRAM 以其高速和大容量的優(yōu)點獲得了極大的應(yīng)用,但是其接口與目前廣泛應(yīng)用的微處理器系統(tǒng)不兼容,介紹了用 VHDL 語言實現(xiàn)的SDRAM與RAM之間的接口控制電路,從而將SDRAM應(yīng)用到微處理器

2011-06-01 15:29:15 57

57 文中在介紹DDR2的工作原理的基礎(chǔ)上,給出了一個用VHDL語言設(shè)計的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統(tǒng)中DDR2 SDRAM的應(yīng)用方案,同時在Virtex-5系列的FPGA上得到了實現(xiàn)

2011-07-23 10:03:16 5102

5102 文章對適用DDR2 SDRAM控制器的結(jié)構(gòu)、接口和時序進行了深入研究與分析,總結(jié)出一些控制器的關(guān)鍵技術(shù)特性,然后采用了自頂向下(TOP-IX)WN)的設(shè)計方法,用Verilog硬件描述語言實現(xiàn)控制器,

2011-09-01 16:36:29 174

174 SDRAM存儲芯片擁有快速讀寫的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴格的控制時序和工作狀態(tài),可以使用有限狀態(tài)機理論

2011-10-24 15:08:05 0

0 本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術(shù),并使用VHDL語言設(shè)計實現(xiàn)DRAM控制器。

2012-02-02 11:29:58 1185

1185

通過設(shè)計基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等單片機和DSP等微處理器的外部連接SDRAM,增加系統(tǒng)的存儲空間。

2012-02-16 17:06:47 45

45 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 Xilinx FPGA工程例子源碼:FM收音機的解碼及控制器VHDL語言實現(xiàn)

2016-06-07 14:13:43 11

11 高速圖像存儲系統(tǒng)中SDRAM控制器的實現(xiàn)

2016-08-29 15:02:03 10

10 基于VHDL的SDRAM控制器的實現(xiàn)

2017-01-22 13:43:27 12

12 DDR2SDRAM控制器在機載顯控系統(tǒng)中的應(yīng)用_孫少偉

2017-03-19 11:26:54 1

1 EPM1240的SDRAM控制器的設(shè)計

2017-10-31 08:24:31 21

21 邏輯復雜,接口方式與普通的存儲器差異很大。為了解決這個矛盾,需要設(shè)計專用的SDRAM控制器,使用戶像使用SRAM -樣方便的使用SDRAM。考慮到控制器的通用性,本文中提出了一種通用的SDRAM控制器的FPGA設(shè)計,F(xiàn)PGA內(nèi)部采用狀態(tài)機的方式。該設(shè)計采用了AD公

2017-11-28 19:51:26 5

5 隨著大規(guī)模集成電路和高速、低功耗、高密度存儲技術(shù)的發(fā)展,SDRAM動態(tài)存儲器因容量大、速度快、價格低廉等優(yōu)點,現(xiàn)已成為PC內(nèi)存的主流。然而SDRAM存儲器內(nèi)部控制邏輯十分復雜,時序要求也非常嚴格,因此需要設(shè)計專門的SDRAM控制器來實現(xiàn)系統(tǒng)對SDRAM的訪問。

2018-04-30 10:58:00 5070

5070

SDRAM 具有存儲容量大、速度快、成本低的特點,因此廣泛應(yīng)用于雷達信號處理等需 要海量高速存儲的場合,但是SDRAM 的操作相對復雜,需要有專門的控制器配合處理器 工作完成數(shù)據(jù)的存取操作。隨著FPGA 技術(shù)的快速發(fā)展及其應(yīng)用的普及,用FPGA 實現(xiàn) SDRAM 控制器是目前最流行的技術(shù)手段。

2019-04-26 08:06:00 2129

2129

實現(xiàn)數(shù)據(jù)的高速大容量存儲是數(shù)據(jù)采集系統(tǒng)中的一項關(guān)鍵技術(shù)。本設(shè)計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態(tài)機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

,SDRAM的原理和時序,SDRAM控制器,動態(tài)隨即存儲器SDRAM模塊功能簡介,基于FPGA的SDRAM控制器的設(shè)計和實現(xiàn),一種簡易SDRAM控制器的設(shè)計方法

2018-12-25 08:00:00 56

56 VHDL語言由于其其強大的行為描述能力及與硬件行為無關(guān)的特性,被廣泛的用于數(shù)字系統(tǒng)設(shè)計,實現(xiàn)了硬件電路設(shè)計的軟件化,成為實現(xiàn)Petri網(wǎng)邏輯控制器的有力的工具。用VHDL語言進行數(shù)字電路設(shè)計的很大

2020-09-22 20:46:51 691

691

針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發(fā)式操作進行研究的基礎(chǔ)上,提出一種簡易SDRAM 控制器的設(shè)計方法。該設(shè)計方法充分利用全頁式高效率存取的優(yōu)點,對SDRAM 進行配置、全頁突發(fā)式讀寫時,操作方便。在實現(xiàn)sDRAM 的快速批量存儲方面,具有良好的應(yīng)用價值。

2020-12-18 16:13:18 6

6 本教程介紹如何將Altera的DE2開發(fā)和教育板上的SDRAM芯片與使用Altera SOPC Builder實現(xiàn)的Nios II系統(tǒng)一起使用。本文的討論是基于這樣一個假設(shè):讀者可以訪問DE2板,并且熟悉教程介紹中使用VHDL設(shè)計的Altera SOPC Builder的內(nèi)容。

2021-01-22 15:34:11 9

9 的設(shè)計方法。結(jié)合實際系統(tǒng),設(shè)計給出了使用FPGA實現(xiàn) SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過增加流水級數(shù)和將輸出觸發(fā)器布置在IO單元中,該控制器可達到185MHz的頻率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越來越廣泛。

2.SDRAM具有存儲容量大,速率快的特點。

3.SDRAM對時序要求嚴格,需要不斷刷新保持數(shù)據(jù)。

.FPGA在電子設(shè)計中的廣泛應(yīng)用,使用十分靈活利用FPGA來設(shè)計自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 本應(yīng)用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現(xiàn)的 DDR SDRAM 控制器。該實現(xiàn)運用了直接時鐘控制技術(shù)來實現(xiàn)數(shù)據(jù)采集,并采用自動校準電路來調(diào)整數(shù)據(jù)線上的延遲。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相應(yīng)的解決方案詳細介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設(shè)計方案。該控制器采用Verilog HDL硬件描述語言實現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 在FPGA視頻圖像處理系統(tǒng)中,經(jīng)常需要使用到SDRAM作為視頻圖像緩存。SDRAM控制器可以分為上電初始化,自動刷新,讀操作和寫操作這四個部分,他們之間的轉(zhuǎn)換可以通過狀態(tài)機來控制。下面分別實現(xiàn)這幾個部分。

2021-04-19 09:46:24 3460

3460

,SDRAM的控制邏輯復雜,使用很不方便。 為了解決這個矛盾,需要設(shè)計專用的SDRAM控制器,使系統(tǒng)用戶象使用SRAM一樣方便的使用SDRAM是十分必要的。考慮到控制器的通用性,本文提出了一種通用的SDRAM控制器的 Verilog設(shè)計,并給出了實現(xiàn)結(jié)果。 1 SDRAM的工作原理

2021-06-30 09:16:47 2346

2346

基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)簡介(arm嵌入式開發(fā)平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介(嵌入式開發(fā)工程師和基層公務(wù)員)-該文檔為基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語言VHDL實現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過一個液位控制系統(tǒng)實例具體介紹了這一方法,并通過仿真波形證明了該方法的正確性。這對于離散事件系統(tǒng)并行控制器的設(shè)計具有十分重要的意義。

2023-08-03 15:33:38 299

299

實時視頻SDRAM控制器的FPGA設(shè)計與實現(xiàn)

2022-12-30 09:21:26 3

3 電子發(fā)燒友網(wǎng)站提供《基于VHDL的洗衣機控制器的設(shè)計.pdf》資料免費下載

2023-11-07 10:28:58 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評論