在高速實時或者非實時信號處理系統當中,使用大容量存儲器實現數據緩存是一個必不可少的環節,也是系統實現中的重點和難點之一。SDRAM(同步動態隨機訪問存儲器)具有價格低廉、密度高、數據讀寫速度快的優點,從而成為數據緩存的首選存儲介制裁。但是SDRAM存儲體結構與RAM有較大差異,其控制時序和機制也較復雜,限制了SDRAM的使用。目前,雖然一些能家長微處理器提供了和SDRAM的透明接口,但其可擴展性和靈活性不夠,難以滿足現實系統的要求,限制了SDRAM的使用。

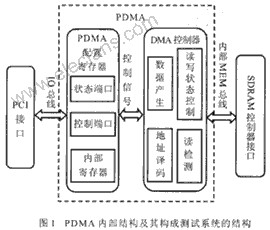

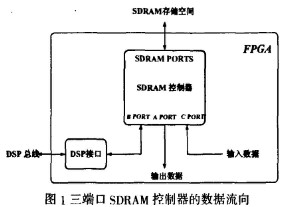

在詳細闡讀SDRAM數據文檔的前提下,參考ALTERA公司的IP core,利用可編程器件(CPLD,FPGA)設計了一種通用的SDRAM控制器。它具有很高的靈活性,可以方便地和其它數據采集分析系統中,如圖1所示。在該系統中,以SDRAM存儲陣列緩存中頻來的高速數據。存滿后,數據被慢速讀出至數據處理模塊。下面將對SDRAM控制模塊的設計進行詳細的描述。

1 SDRAM內存條的結構

SDRAM內存條由SDRAM內存芯片構成,根據內存條的容量大小決定內存條上內存芯片的個數。現以MICRON公司生產的TIM16LSDT6464A型SDRAM內存條為例,簡要介紹SDRAM的結構。

MIT16LSDT6464A內存條容量為512M Byte,由16片容量為32M Byte的內存芯片MT46LC32M8A2構成。16片內存芯片被分為兩級,每個芯片的數據位寬為8bit.8片一組,64bit數據寬度。每個內存芯片的數據線和控制均是復用的。對內存條的讀寫操作,是以內存芯片組為單位的,通過內存條的片選信號S0、S1、S2、S3決定組號。S0、S2控制芯片組1,S1、S3控制芯片組2.

SDRAM內存芯片的主要信號有控制信號、控制信號、數據信號,均為工作時鐘同步輸入、輸出信號。

控制信號主要有:CS(片選信號),CKE(時鐘使能信號),DQM(輸入、輸出使能信號),CAS、RAS、WE(讀寫控制命令字)。通過CAS、RAS、WE的各種邏輯組合,可產生各種控制命令。

地址信號有:BA0和BA1頁地址選擇信號,A0~A12地址信號,行、列地址選擇信號。通過分時復用決定地址是行地址還是列地址。在讀寫操作中,在地線上依次給出頁地址、行地址、列地址,最終確定存儲單元地址。

數據信號有:DQ0~DQ7,雙向數據。其使能受DQM控制。

SDRAM的工作模式通過LOAD MODE REGISTER命令對工作模式寄存器進行設置來選擇。設置參量有Reserved(備用的人)Write Burst Mode(WB,寫突發模式)、Operation Mode(Op Mode,工作模式)、CAS Latency(CAS延遲)、Burst Type(BT,突發類型)、Burst Length(突發長度)。

2 SDRAM的基本讀寫操作

SDRAM的基本讀操作需要控制線和地址線相配合地發出一系列命令來完成。先發出BANK激活命令(ACTIVE),并鎖存相應的BANK地址(BA0、BA1給出)和行地址(A0~A12給出)。BANK激活命令后必須等待大于tRCD(SDRAM的RAS到CAS的延遲指標)時間后,發出讀命令字。CL(CAS延遲值)個工作時鐘后,讀出數據依次出現在數據總線上。在讀操作的最后,要向SDRAM發出預充電(PRECHARGE)命令,以關閉已經激活的頁。等待tRP時間(PRECHARGE)命令,以關閉已經激活的頁。等待tRP時間(PRECHAREG命令后,相隔tRP時間,才可再次訪問該行)后,可以開始下一次的讀、寫操作。SDRAM的讀操作只有突發模式(Burst Mode),突發長度為1、2、4、8可選。

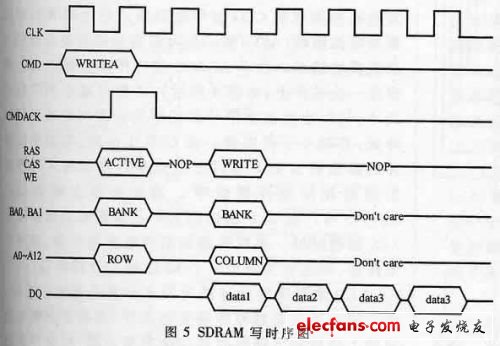

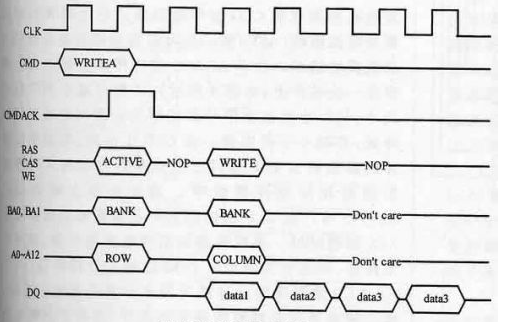

SDRAM的基本寫操作也需要控制線和地址線相配合地發出一系列命令來完成。先發出BANK激活命令(ACTIVE),并鎖存相應的BANK地址(BA0、BA1給出)和行地址(A0~A12給出)。BANK激活命令后必須等待大于tRCD的時間后,發出寫命令字。寫命令可以立即寫入,需寫入數據依次送到DQ(數據線)上。在最后一個數據寫入后延遲tWR時間。發出預充電命令,關閉已經激活的頁。等待tRP時間后,可以展開下一次操作。寫操作可以有突發寫和非突發寫兩種。突發長度同讀操作。

tRCD、tRP、tWR的具體要求,詳見SDRAM廠家提供的數據手冊。所等待的工作時鐘個數由tRCD、tRP、tWR的最小值和工作時鐘周期共同決定。

由以上介紹可以得出,SDRAM的讀、寫操作均由一系列命令組成,因此讀、寫操作是有時鐘損耗的,工作時鐘速率不等于SDRAM能達到的讀、寫速率。但是由于SDRAM有突發讀、寫模式,也就是說可以讀出和寫入一串地址連續的數據,從而提高了效率。當突發長度為整頁時,讀、寫速度達到最快。隨機讀、寫速度的計算公式為:

furite/read=工作時鐘頻率(HzHzHhdkkdk ss dkkdkdkd,,,m,mddddd)×數據寬度(bytes)×突發讀寫長度/操作所需的時鐘數

為了提高存儲密度,SDRAM采用硅片電容存儲信息。電容總會有漏電流流過,所以為了不使信息丟失,必須定期地給電容刷新充電。外部控制邏輯必須按要求定期向內存條發出刷新命令,保證在規定的時間內對每一個單元都進行刷新。

3 初始化操作

SDRAM在上電以后必須對其進行初始化操作,具體操作如下:

(1)系統在上電后要等待100~200μs.在待時間到了以后至少執行一條空操作或者指令禁止操作。

(2)對所有芯片執行PRECHARGE命令,完成預充電。

(3)向每組內存芯片發出兩條AUTO REFRESH命令,使SDRAM芯片內部的刷新計數器可以進入正常運行狀態。

(4)執行LOAD MODE REGISTER命令,完成對SDRAM工作模式的設定。

完成以上步驟后,SDRAM進入正常工作狀態,等待控制器對其進行讀、寫和刷新等操作。

4 SDRAM控制器設計

4.1 功能說明

在以SDRAM作為緩存的系統中,使用可編程器件對其進行控制具有很強的靈活性。為了使設計具有模塊化和可重復使用的優點,設計了一個簡化的SDRAM接口電路。這樣就屏蔽掉了SDRAM操作的復雜性,而其它邏輯模塊可通過接口電路對SDRAM進行訪問。此外,由于整個SDRAM控制器用VHDL語言編寫,只要對其進行簡單的修改就可以滿足不同的需求,具有很強的靈活性。

參照圖2,SDRAM控制器完成的主要功能是對CMD[2:0]的命令字和ADDR端的地址進行解析,產生相應的SDRAM的控制時序。

CLK為輸入的工作時鐘端口。

ADDR為輸入地址端口。控制器將其解析為對應的片選、頁以及行、列地址。以一條MIT16LSDT6464A內存條為例,其大小為512Mbyte(2 29 byte)。數據位寬為64bit(8byte),則地址線ADDR應為26根。可以這樣映射地址:ADDR[25]對應內存芯片組號;ADDR[24:23]對應頁號;ADDR[22:10]對應行號;ADDR[9:0]對應列號。

DATAIN為寫入數據端口,64bit位寬。

DATAOUT為讀出數據端口,64bit位寬。

RD_OE為讀出數據使能端口,當其為1時,表示從下一個時鐘起,數據將依次出現在DATAOUT口上。

WR_OE為寫入數據使能端口,當其為1時,寫入數據應該依次出現在DATAIN口上。

CMD[2:0]為命令輸入端口,分別表示讀、寫內存等待操作。其中,CMD=“000”表示無操作,內存條交給控制器管理,定其完成刷新工作;REFRESH命令由外部邏輯指定特刷新的內存芯片信號,組號由ADDR的低位給出;LOAD_MODE命令執行內存條工作寄存器初始化工作,初始化值由DATAIN的低13位決定,內存芯片組號同樣由ADDR的低位給出;同理,ADDR的低位也決定了預充電操作所對應的內存芯片組號。

CMDACK為命令應答端口,表示命令已經被執行,使外部邏輯可以向控制器發出下一個動作。

4.2 狀態機

圖3是SDRAM控制器的狀態轉移圖。狀態圖中的各個狀態內均包含一系列的子狀態轉移(對SDRAM內存條發出連續命令),每個子狀態完成一個功能操作。初始化操作包括前面介紹的內存條初始化全過程,工作寄存器的默認值在VHDL程序中指定。以后可以通過LOAD_MODE命令改變內存條的工作模式。初始化結束后,內存條進入Idel狀態,刷新計數器開始工作,控制器開始響應外部邏輯的操作請求。

刷新計數器操作是一個獨立的進程(process)。刷新計數器的初值由內存芯片要求、內存條個數和控制器工作頻率共同決定。例如,在本次設計中,所采用的MT48LC32M8A2內存芯片要求在64ms內夏至少刷新8196次。而MIT16LSDT6464A型內存條共有兩組內存芯片,也就是要求在64ms內要發出8196×2條自刷新(AUTO REFRESH)指令。系統工作時鐘為46.66MHz,因此控制單條MIT16LSDT6464A時,刷新計數器初值至多為(64ms/8196/2)×6、、46.66MHz,即182.開始工作后,每當刷新計數器值減為0,便依次向內存芯片組發出刷新命令,保證SDRAM中的數據不丟失。刷新請求是內存請求;讀和寫操作是外部請求。在Idel狀態中有請求仲裁邏輯,當內部和外部請求同時出現時,優先保證內部請求,狀態轉移至刷新操作。當刷新操作結束時,重新返回Idel狀態,開始響應外部請求。響應外部請求后,應答信號CMDBAK出現正脈沖。它通知外部邏輯,請求已經被響應,可以撤銷請求。在刷新操作狀態中,也有許數器計數,其大小等于控制器管理的內存芯片信號。記錄并判斷此次刷新操作所對應的內存芯片的組號,產生相應的片選信號。

響應讀、寫請求后,狀態從Idel轉移到讀、寫狀態。同時讀、寫地址和寫入的數據鎖存至控制器。控制器由讀寫地址解析出CS信號、頁地址、行地址、列地址。向內存條發出一系列命令(ACTIVE,READ/WRITE with AUTO PRECHARGE),完成讀寫操作,為了簡化,此控制器向SDRAM發出的都是帶有AUTO PRECHARGE的讀、寫指令,然后由SDRAM內部邏輯自動在讀、寫過程末期發出PRECHARGE指令(在發READ/WRITE指令時,地址線A10賦值1,打開AUTO PRECHARGE功能)。圖4和圖5分別是利用該控制器完成讀、寫操作的時序圖。讀操作的CAS延遲為兩個時鐘。

該SDRAM控制器在中頻數據海量存儲系統中已得到應用。數據接收邏輯將接收到的中頻采樣數據整理后(拼接成64bit),通過SDRAM控制器存入SDRAM陣列。存滿后,數據輸出邏輯將中頻數據通過SDRAM控制器從內存條中取出,傳輸至上位機。其VHDL代碼在ATERA公司的FPGA--EP1C6Q240中通過了Quartus II的仿真、綜合和布局、布線。占用499個logic cellk,消耗了8%的邏輯資源。留有豐富的資源可提供給其它邏輯單元使用。

上面介紹了SDRAM的基本工作原理和一種簡單的通用SDRAM控制器的實現。SDRAM的控制機制比較復雜,具有多種突發讀、寫方式和工作模式(詳細內容請參考SDRAM的數據手冊)。但是,可以根據實現應用,實現其中的一個子集(基本讀、寫、刷新操作)來滿足實際系統的需要。用SDRAM實現大容量的高速數據緩存具有明顯的優勢,使用可編程器件實現SDRAM控制器則使之具有更高的靈活性,其應用前景廣闊。

?

電子發燒友App

電子發燒友App

評論