汽車音響導航系統中DDR高速信號的PCB設計

2012年02月06日 10:51 來源:《科技創新導報》 作者:王文靜 我要評論(0)

在以往汽車音響的系統設計當中, 一塊PCB上的最高時鐘頻率在30~50MHz已經算是很高了,而現在多數PCB的時鐘頻率超過100MHz,有的甚至達到了GHz數量級。為此,傳統的以網表驅動的串行式設計方法已經不能滿足今天的設計要求, 現在必須采用更新的設計理念和設計方法,即將以網表驅動的串行的設計過程, 改變成將整個設計各環節并行考慮的一個并行過程。也就是說將以往只在PCB布局、布線階段才考慮的設計要求和約束條件, 改在原理圖設計階段就給予足夠的關注和評估,在設計初期就開始分析關鍵器件的選擇,構想關鍵網線的拓撲結構, 端接匹配網絡的設定, 以及在布線開始前就充分考慮PCB的疊層結構,減免信號間的串擾方法,保證電源完整性和時序等因素。

本文主要介紹在汽車音響導航系統中使用的高速DDR200,在兼顧高速電路的基本理論和專業化設計經驗的指導下, 保證信號完整性的PCB設計方法。

1 什么是DDR 及其基本工作原理

DDR SDRAM, 習慣稱為DDR.DDR SDRAM即雙倍速率同步動態隨機存儲器。

DDR內存是在SDRAM 內存基礎上發展而來的。SDRAM在一個時鐘周期內只傳輸一次數據, 它是在時鐘的上升期進行數據傳輸;而DDR內存則是一個時鐘周期內傳輸兩次數據, 它能夠在時鐘的上升期和下降期各傳輸一次數據,因此稱為雙倍速率同步動態隨機存儲器。DDR內存可以在與SDRAM相同的總線頻率下達到雙倍的數據傳輸率。

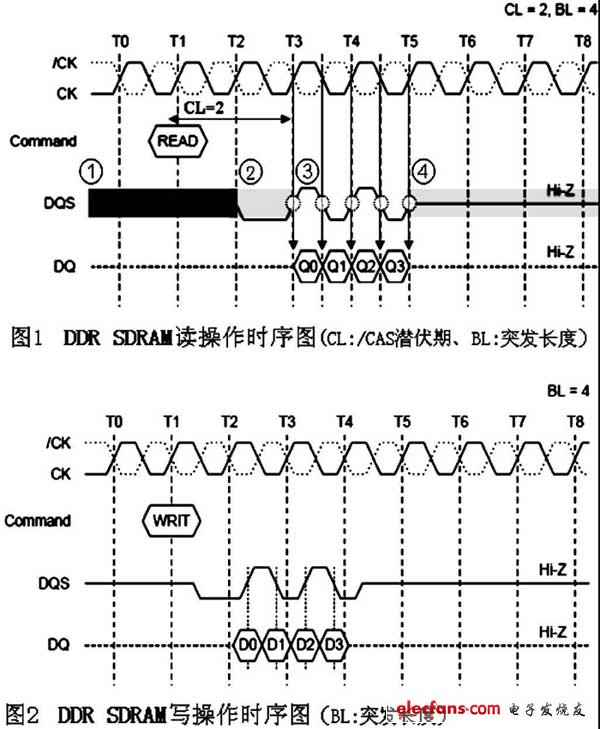

如下圖1和圖2所示,DDR SDRAM相對SDRAM多了兩個信號: CLK# 與DQS。

CLK# 與正常CLK時鐘相位相反, 形成差分時鐘信號。而數據的傳輸在CLK與CLK# 的交叉點進行, 即在CLK的上升與下降沿(此時正好是CLK#的上升沿)都有數據被觸發,從而實現雙倍速率傳輸。

DQS(DQ STrobe、數據選取脈沖)是DDRSDRAM中的重要功能, 主要用來在一個時鐘周期內準確的區分出每個傳輸周期,并在接收端使用DQS來讀出相應的數據DQ。

DQS在上升沿和下降沿都有效,與數據信號同時生成。DQS和DQ都是三態信號雙向傳輸。在讀操作時,DQS信號的邊沿在時序上與DQ 的信號邊沿處對齊, 而寫操作時,DQS信號的邊沿在時序上與DQ信號的中心處對齊。

下面以圖1-DDR SDRAM讀操作時序圖為例,說明DQS的控制原理:

①在沒有數據輸出的狀態時,DQS處于高阻抗水平。

② 接到READ指令后,DQS信號變為低阻抗, 并較數據輸出時間提前一個周期。

③ D Q S 信號在CLK與CLK# 的交叉點與數據信號同時生成,頻率與CLK相同。

④DQS信號持續到讀脈沖突發完了為止, 完了后再度恢復到高阻抗水平。

2 基本規格

DDR SDRAM的基本規格(表1)。

表1 DDR SDRAM的基本規格

3 DDR200 的PCB 設計方法

下面以汽車音響導航系統中使用的DDR200為例,從PCB疊層結構的選擇、布線拓撲結構、串擾、電源完整性和時序等方面考慮的PCB設計方法。

3.1 PCB疊層結構的選擇

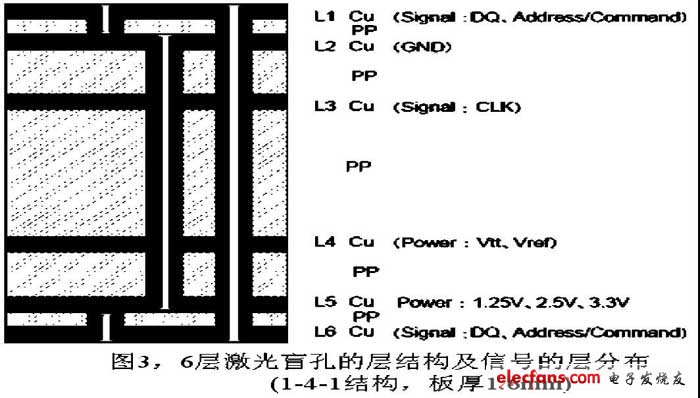

線路板的疊層結構直接決定了信號在各導體層的傳輸速度及延遲時間。根據電路構成及結構限制,結合高速信號及電源的返回路徑等EMI要求,在設計初期確定好疊層結構以及重要信號的布線層是十分重要的。本例的疊層結構及重要信號的布線層如圖3 所示。

根據板材不同, 導體銅厚, 各絕緣層厚及介電常數等也會有差異,導致高速信號傳輸線的特性阻抗Zo及傳輸延時Tpd的不同。

板材中絕緣介質的介電常數εr=4.0,絕緣層厚PP1=60μm,PP2=200μm,PP3=800μm,導體銅厚35μm,且線寬W=100μm時,信號在表層(L1、L6)的傳輸延時Tpd≒140ps,特性阻抗Zo≒56Ω,在內層L3布線的傳輸延時Tpd≒170ps,特性阻抗Zo≒84Ω。

本文導航

- 第 1 頁:汽車音響導航系統中DDR高速信號的PCB設計(1)

- 第 2 頁:DDR SDRAM信號的布線標準

- 第 3 頁:Address/Command的布線方法