?

傳真通信規程是將要掃描的電平信號值進行A/D轉換,再經過圖像二值化處理,表示成連續交替黑白點的數據序列(I/O序列),再對該數據序列進行編碼后,調制發送;接收端對收到的編碼數據信號解調后進行譯碼,最后由熱敏頭打印輸出。

在傳真通信中,對傳真圖像數據進行編碼和譯碼是傳真通信的關鍵技術。改進的Huffman碼(MHC)是ITU—T.4向各國推薦的一維標準碼,主要應用于三類傳真機上。MHC碼是一種常用的變長碼,其信源的消息與碼字之間的關系是一對一的,是信息保持型的壓縮方法。雙網傳真系統完成與Internet和PSTN網絡的傳真通信,采用嵌入式系統的設計思路劃分軟硬件。其中,傳真協議采用軟件實現,傳真編譯碼和外圍設備控制器采用硬件實現,以降低設計復雜度,提高傳真效率。

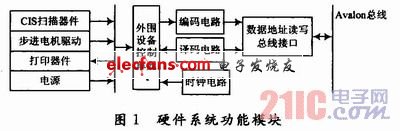

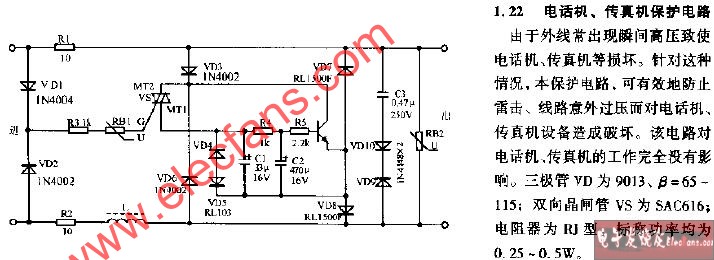

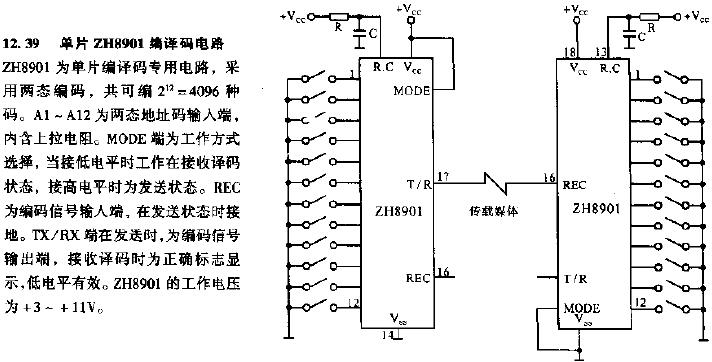

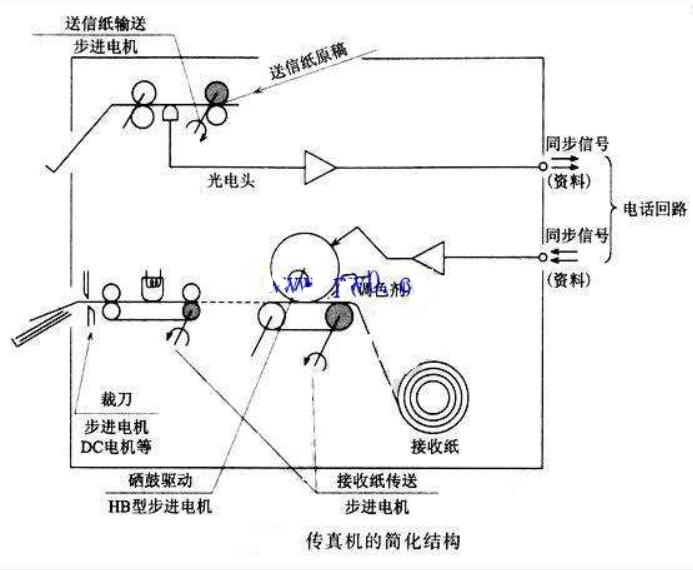

1 傳真機硬件系統模型

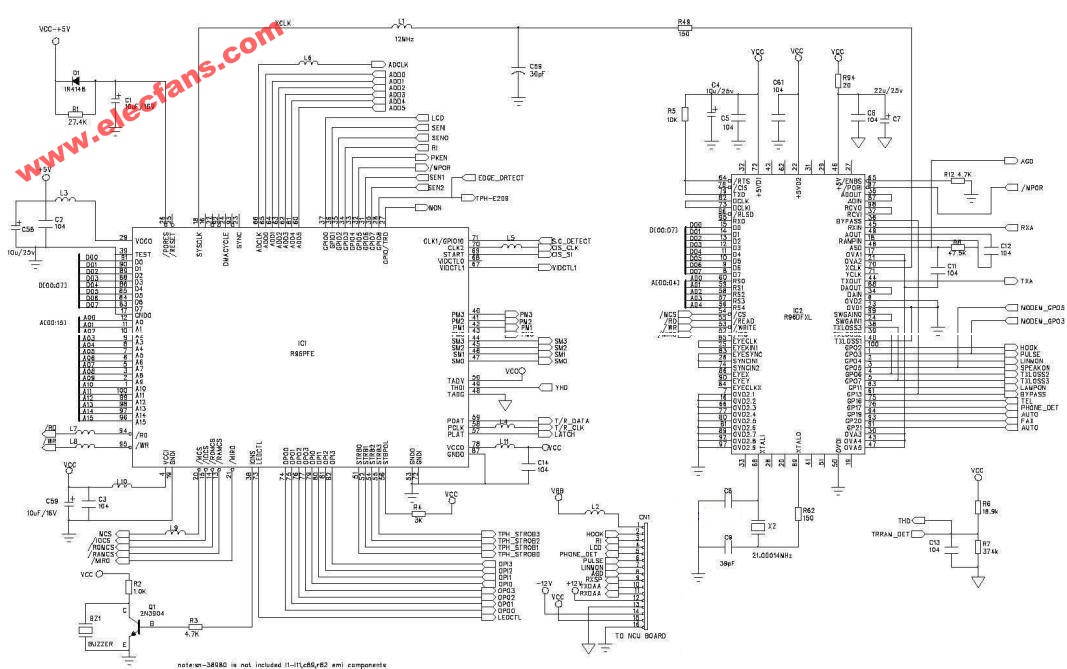

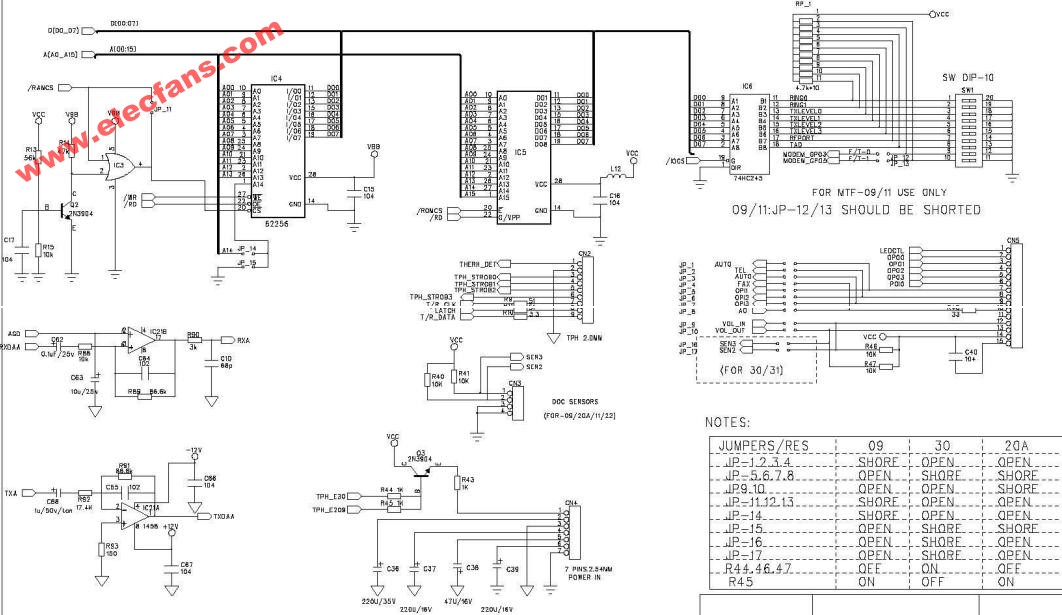

硬件電路模塊應包括:CIS掃描電路模塊(A/D轉換)、編碼電路模塊(圖像二值化處理)、譯碼電路模塊、打印電路模塊、步進電機驅動電路模塊及時鐘電路模塊。并以NiosⅡ軟核處理器、CIS掃描器件、步進電機、TPH打印器件為硬件平臺,通過FPGA實現硬件電路模塊。上層軟件通過讀寫寄存器來控制外圍設備和編譯碼電路,完成編碼數據的讀取和譯碼數據的寫入。圖1給出了硬件系統功能模塊劃分邏輯圖。

?

其中,時鐘電路用來產生掃描、打印及步進電機所需的時序信號;由時鐘電路產生的CIS時鐘周期為2.6μs,打印時鐘周期為4.96μs,步進電機時鐘周期為10 ms。數據地址讀寫總線接口與NiosⅡ處理器直接交互各種控制命令及讀寫數據,產生外圍設備的工作使能信號,通過地址選通信號,完成各個模塊與NiosⅡ處理器之間數據的交互。

2 外圍設備控制單元

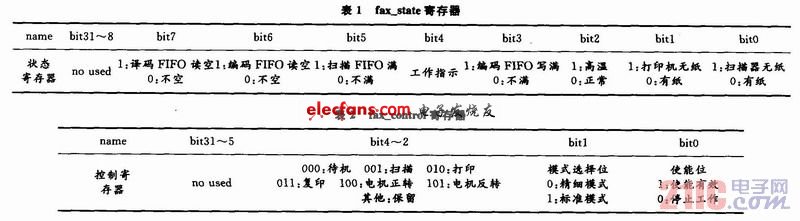

外圍設備的控制主要是通過對CIS掃描器件、TPH打印器件和步進電機發出相應的控制時序信號完成掃描、打印和步進電機的驅動等功能。該部分采用硬件實現可以產生超過定時中斷周期的更小周期的時序信號和時序要求精確的驅動信號,同時可以通過配置控制寄存器,對掃描和打印的功能進行選擇,上層軟件通過狀態寄存器來判斷電路的工作狀態。表1和表2給出了寄存器的詳細描述。

?

2.1 CIS掃描及A/D轉換

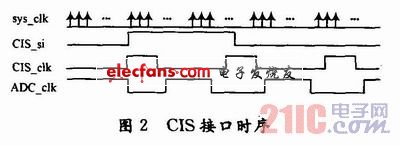

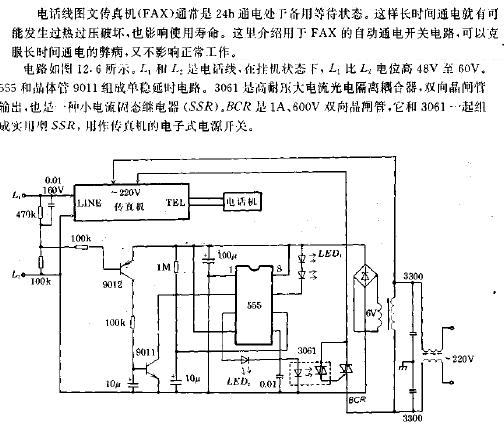

設計采用的CIS器件具有最高1.7 MHz的掃描時鐘,且有效掃描寬度為216 mm(A4紙的寬度),每行有1728個掃描點。FPGA片內的數字邏輯產生驅動信號CIS_si和CIS_clk,并將模擬信號接入A/D轉換器的模擬輸入端口,由FPGA片內數字邏輯實時對A/D轉換器的輸出進行采集。圖2給出了CIS接口時序。其中,CIS_si為行啟動信號,每行有1728個掃描點,每隔10ms啟動一次CIS_si。由于掃描最快能達到1.8ms/line,而打印最快只能達到10 ms/line,所以掃描完成后且預留出步進電機工作的時間,這樣就能滿足該系統的要求。CIS_clk為2.6μs的掃描時鐘,占空比為0.254。ADC_clk為AD采樣時鐘,周期與CIS_clk相同,占空比為0.046。

?

A/D轉換的原理是通過CIS掃描器件把原稿的光信號轉化為電信號,將CIS掃描器件獲得的模擬電信號通過A/D轉換器件轉化為8 b的數字信號在ADC_clk的下降沿送入掃描數據緩沖區。

2.2 步進電機控制

在傳真機硬件系統中,步進電機的主要作用是根據當前工作狀態,驅動掃描或打印夾紙的滾軸。步進電機的時鐘周期為10 ms,滿足系統要求。掃描時步進電機反轉,打印時正轉。通過控制寄存器,可以實現標準和精細兩種掃描模式。

2.3 打印器件

設計所用的熱敏打印器件系統采用SHECHA216-UH,其接口時序如圖3所示(data表示數據在鎖存信號有效后輸出)。其中,heater_clk為打印頭時鐘,1 MHz,50 %占空比;heater_latch_n為打印頭鎖存信號,低電平有效,每隔10ms鎖存一次;heater_trobe[3:0]為打印頭加熱段選信號,在10 ms內,這四個信號依次低有效一次。

?

3 編碼電路單元設計

對一個二值傳真信源來說,一副傳真圖像是由掃描線上的像素組成的,而每一掃描線又總是由一些連續的黑像素和白像素組成,連續發生的黑像素為連‘1’,白像素為連‘0’,也稱之為黑游程和白游程。連‘1’的個數稱為黑游程長度,連‘0’的個數稱為自游程長度。黑白游程總是交替出現的。游程長度就等于一條掃描線上的像素總數,A4幅面一般為1 728。本項目使用的圖像二值化方法是固定閾值法,即將A/D轉化后的8 b數據和閾值做比較,得到‘0’或‘1’(白點或黑點)。當總線地址為01H時,讀取32位編碼寄存器。

無失真的信源編碼方式中,使用最多的是變長碼,其中最優的編碼是Huffman碼,改進的Huffman碼(MHC)是三類傳真機信源編碼的標準。MHC所做的主要改進是將碼字分為終止碼和形成碼,能夠用較短的編碼來表示較長的連續黑點或自點。0~63的游程長度用終止碼表示,64整數倍的游程長度由形成碼表示,任意游程長度大于63的碼字表示為“形成碼+終止碼”。例如,當白游程長度為131 b(128+3)時,編碼表示為‘100101000’,即,白游程長度128 b的形成碼‘10010’加上白游程長度為3 b的終止碼‘1000’。行同步碼EOL的格式為‘0000000000 01’。WRLC為白游程長度編碼,BRLC為黑游程長度編碼。每一行的第一個游程長度編碼為白碼字,黑白游程長度碼字連續交替。收到連續的六個EOL后表示該頁結束。根據T.4的表述,一頁編碼后的傳真數據格式如表3所示。

?

在構建碼表時,構建四個不同的碼表單元,即黑、白游程形成碼碼元單元和黑、白游程終止碼碼元單元。同時需要存儲黑白游程編碼碼元的長度信息。終止碼碼表的地址是按游程長度編寫的,即0~63,而形成碼的碼表地址共有27個。這樣存儲可以通過黑白計數值直接找到地址,碼表所存儲的信息為17位,表4給出了MHC碼表的輸出說明。

?

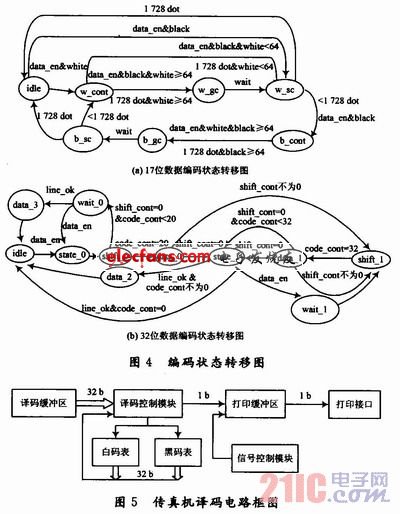

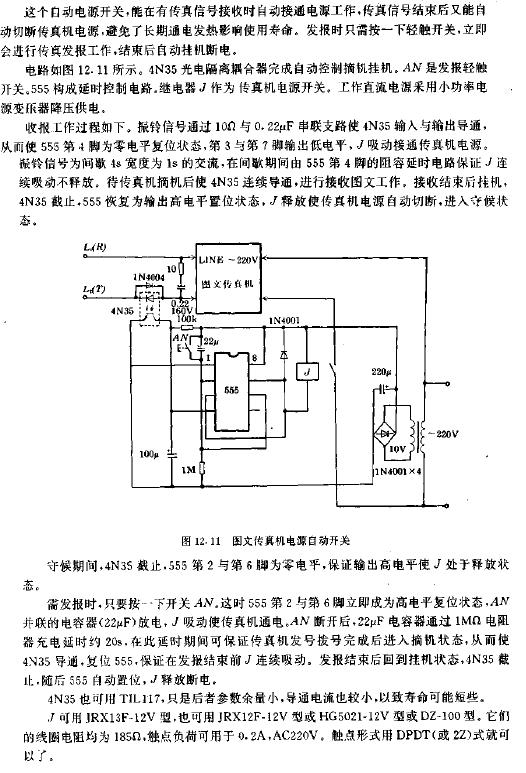

例如,編碼得到的碼元信息是‘0111’,這是白游程2所代表的碼元,則碼元的有效長度為‘0100’(4位),碼元信息為‘011100000000 0’(13位)。在碼元黑白屬性發生改變時,如果當前游程的計數長度小于64,則取計數長度的低6位為地址,查找對應碼表(終止碼表)中的17位數據;如果游程長度大于或等于64,則取計數長度的高5位為地址,查找對應碼表(形成碼表)中的17位數據。NiosⅡ處理器進行數據交換,采用32位寄存器接口。每次查找完MHC碼表后,采用二級編碼電路對一級編碼電路得到的信息再進行一次編碼,將17位編碼數據轉換成32位編碼數據。圖4給出了編碼狀態轉移圖。

?

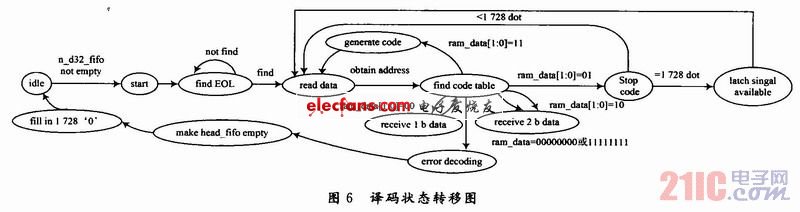

4 譯碼電路單元設計

對于MHC碼而言,首先它是一個變長碼,發送端在編碼時把游程長度所對應的碼元數據不留間隙的存入發送緩沖區中,經過調制載波后發送出去。接收端解調出來的數據,即編碼數據,譯碼時從該數據序列中分離出碼字,由碼字去找出所對應的游程長度,輸出到打印緩沖區,就完成了譯碼過程。要提高譯碼速度,可以采用多步合一的方法,減少查找碼表的次數,也就是一次輸入多個碼元。根據碼表的特點,對白譯碼而言,第一次可直接輸入4個碼元,對于黑譯碼,第一次可輸入2個碼元,隨后每次可輸入2個碼元或1個碼元。

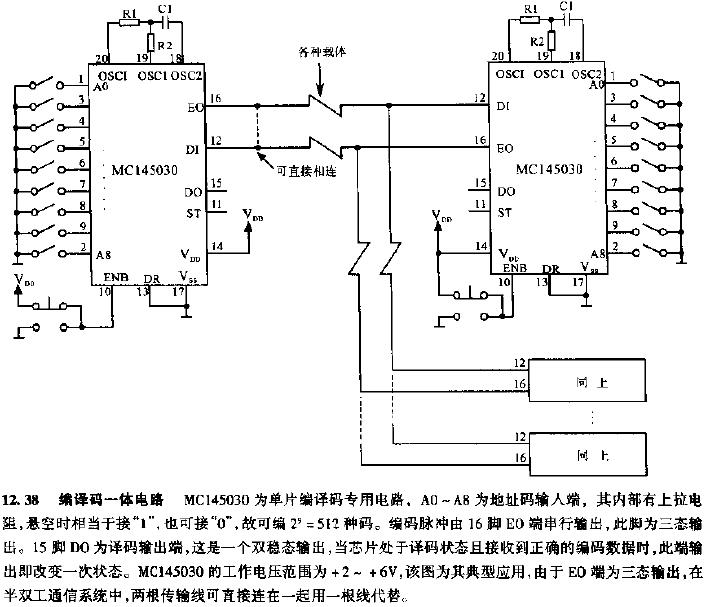

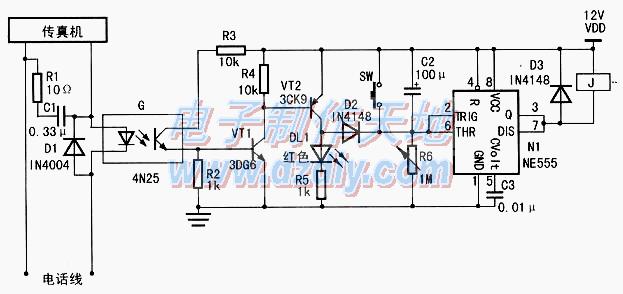

譯碼時,通過Avalon總線接口將編碼數據寫入一個32×256 b的緩沖區;譯碼完成后,將數據送到打印緩沖區,由信號控制模塊控制打印緩沖區的復位、讀時鐘、讀請求和打印頭時鐘信號,打印緩沖區的大小為1×2 048 b。當寫入個數記到1 728時,就會進行讀操作。如果出現誤碼,寫入個數超過1 728時,FIFO清零,此時不進行讀操作,而是將誤碼的那行數據丟棄,并加入一行白點(1 728個‘0’)。傳真譯碼電路如圖5所示。

在譯碼電路中,檢測到EOL后,將對譯碼緩沖區的數據交替地進行白譯碼、黑譯碼、白譯碼操作。其中譯碼碼表的地址和數據寬度均為8 b。譯碼時,接收4 b數據(白碼元),通過形成的8 b地址來查找碼表并返回一個8 b數據Ram_Data,并根據此數據低2位的值來進行下一步操作。當Ram_Data低2位為‘01’時,輸出數據高6位的值,此時終止碼使能有效;當Ram_Data低2位為‘11’時,輸出數據高6位的值,此時形成碼使能有效;當Ram_Data低2位為‘00’時,表示接收1 b數據和Ram_Data相加形成新地址;當Ram_Data低2位為‘10’時,表示接收2 b數據和Ram_Data相加形成新地址;繼續查找碼表,重復操作,直到譯出碼元或出錯為止。查找黑白碼表不同的是:對于白譯碼而言,由于最短碼字長度為4,所以第一次可直接查找4 b碼元,隨之可查找2 b或1 b碼元;而對于黑譯碼而言,由于最短的碼字長度為2,所以第一次查找2 b碼元,隨之可查找2 b或1 b碼元;輸出的6 b數據為連續黑點或連續白點的個數。將譯碼后的數據存入1×2 048 b的打印緩沖區,當存儲數據滿一行時,輸出到打印頭打印,待清空后再進行下一行的譯碼。掃描到打印一行的時間要求是10 ms,所以譯碼完成后進行等待,直到數據鎖存后再進行下一行的譯碼。譯碼狀態轉移圖如圖6所示。

?

5 仿真驗證與系統測試

采用基于碼表遍歷的驗證策略,對電路進行仿真驗證,并查看輸出波形圖,結果均與設計要求一致。仿真部分波形圖如圖7所示。

?

其中,fifo_data為編碼數據;dot_cont為譯出的總點數;white_black_flag為黑白標志位,‘1’表示黑,‘0’表示白。

該電路通過QuartusⅡ環境下的SOPC配置CPU核,在Altera公司的FPGA開發板上進行下載,并在NiosⅡ開發環境中使用軟件測試該電路,通過寄存器驅動電路工作,經過掃描,CPU核向電路寫入編碼數據,待輸出標識位有效后,再讀出譯碼后數據,通過傳真機打印出來。綜合結果表明電路可以工作在100 MHz時鐘頻率下。

將傳真標準樣張編碼數據送給譯碼模塊完成對譯碼電路的測試,打印出的圖像滿足測試標準。然后將標準樣張原稿經過掃描編碼,送給譯碼打印,輸出打印結果與原稿比對。通過反復調試,軟硬件運行穩定,達到系統功能指標。

6 結語

本文采用兩級編碼和快速譯碼的設計思路,在FPGA芯片上實現了編譯碼電路和外設控制器。上層軟件通過寄存器接口完成對硬件系統的控制,經過仿真驗證與測試,電路對傳真數據正確編譯碼,與軟件系統相配合為高性能的雙網傳真機提供了可靠的技術基礎。

電子發燒友App

電子發燒友App

評論